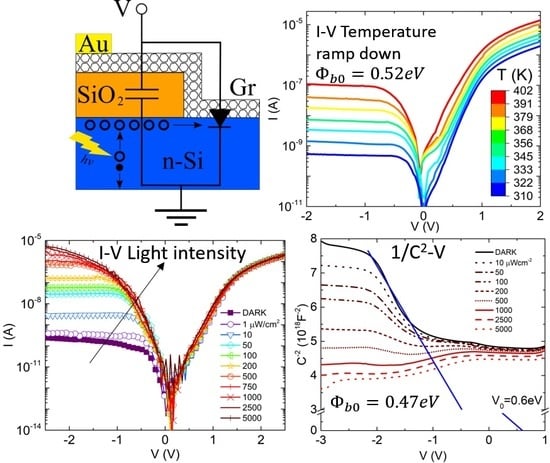

I-V and C-V Characterization of a High-Responsivity Graphene/Silicon Photodiode with Embedded MOS Capacitor

Abstract

:1. Introduction

2. Results and Discussion

3. Materials and Methods

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Pop, E.; Varshney, V.; Roy, A.K. Thermal properties of graphene: Fundamentals and applications. MRS Bull. 2012, 37, 1273–1281. [Google Scholar] [CrossRef]

- Castro Neto, A.H.; Guinea, F.; Peres, N.M.R.; Novoselov, K.S.; Geim, A.K. The electronic properties of graphene. Rev. Mod. Phys. 2009, 81, 109–162. [Google Scholar] [CrossRef]

- Di Bartolomeo, A.; Santandrea, S.; Giubileo, F.; Romeo, F.; Petrosino, M.; Citro, R.; Barbara, P.; Lupina, G.; Schroeder, T.; Rubino, A. Effect of back-gate on contact resistance and on channel conductance in graphene-based field-effect transistors. Diam. Relat. Mater. 2013, 38, 19–23. [Google Scholar] [CrossRef]

- Di Bartolomeo, A.; Giubileo, F.; Romeo, F.; Sabatino, P.; Carapella, G.; Iemmo, L.; Schroeder, T.; Lupina, G. Graphene field effect transistors with niobium contacts and asymmetric transfer characteristics. Nanotechnology 2015, 26, 475202. [Google Scholar] [CrossRef] [PubMed]

- Giubileo, F.; di Bartolomeo, A. The role of contact resistance in graphene field-effect devices. Prog. Surf. Sci. 2017, 92, 143–175. [Google Scholar] [CrossRef]

- Xia, F.; Perebeinos, V.; Lin, Y.; Wu, Y.; Avouris, P. The origins and limits of metal? Graphene junction resistance. Nat. Nanotechnol. 2011, 6, 179–184. [Google Scholar] [CrossRef] [PubMed]

- Di Bartolomeo, A.; Giubileo, F.; Iemmo, L.; Romeo, F.; Russo, S.; Unal, S.; Passacantando, M.; Grossi, V.; Cucolo, A.M. Leakage and field emission in side-gate graphene field effect transistors. Appl. Phys. Lett. 2016, 109, 023510. [Google Scholar] [CrossRef]

- Niu, G.; Capellini, G.; Hatami, F.; di Bartolomeo, A.; Niermann, T.; Hussein, E.H.; Schubert, M.A.; Krause, H.-M.; Zaumseil, P.; Skibitzki, O.; et al. Selective Epitaxy of InP on Si and Rectification in Graphene/InP/Si Hybrid Structure. ACS Appl. Mater. Interfaces 2016, 8, 26948–26955. [Google Scholar] [CrossRef] [PubMed]

- Bonaccorso, F.; Sun, Z.; Hasan, T.; Ferrari, A.C. Graphene photonics and optoelectronics. Nat. Photonics 2010, 4, 611–622. [Google Scholar] [CrossRef]

- Di Bartolomeo, A. Graphene Schottky diodes: An experimental review of the rectifying graphene/semiconductor heterojunction. Phys. Rep. 2016, 606, 1–58. [Google Scholar] [CrossRef]

- Liang, S.J.; Hu, W.; di Bartolomeo, A.; Adam, S.; Ang, L.K. A modified Schottky model for graphene-semiconductor (3D/2D) contact: A combined theoretical and experimental study. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016. [Google Scholar] [CrossRef]

- Varonides, A. Combined thermionic and field emission reverse current for ideal graphene/n-Si Schottky contacts in a modified Landauer formalism. Phys. Status Solidi C 2016, 13, 1040–1044. [Google Scholar] [CrossRef]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; Wiley-Interscience: Hoboken, NJ, USA, 2007; ISBN 978-0-471-14323-9. [Google Scholar]

- Card, H.C.; Rhoderick, E.H. Studies of tunnel MOS diodes I. Interface effects in silicon Schottky diodes. J. Phys. D Appl. Phys. 1971, 4, 1589–1601. [Google Scholar] [CrossRef]

- Cheung, S.K.; Cheung, N.W. Extraction of Schottky diode parameters from forward current-voltage characteristics. Appl. Phys. Lett. 1986, 49, 85–87. [Google Scholar] [CrossRef]

- Di Bartolomeo, A.; Luongo, G.; Giubileo, F.; Funicello, N.; Niu, G.; Schroeder, T.; Lisker, M.; Lupina, G. Hybrid graphene/silicon Schottky photodiode with intrinsic gating effect. 2D Mater. 2017, 4, 025075. [Google Scholar] [CrossRef]

- Di Bartolomeo, A.; Giubileo, F.; Luongo, G.; Iemmo, L.; Martucciello, N.; Niu, G.; Fraschke, M.; Skibitzki, O.; Schroeder, T.; Lupina, G. Tunable Schottky barrier and high responsivity in graphene/Si-nanotip optoelectronic device. 2D Mater. 2017, 4, 015024. [Google Scholar] [CrossRef]

- Riazimehr, S.; Kataria, S.; Bornemann, R.; Haring Bolívar, P.; Ruiz, F.J.G.; Engström, O.; Godoy, A.; Lemme, M.C. High Photocurrent in Gated Graphene–Silicon Hybrid Photodiodes. ACS Photonics 2017, 4, 1506–1514. [Google Scholar] [CrossRef]

- Chen, Z.; Cheng, Z.; Wang, J.; Wan, X.; Shu, C.; Tsang, H.K.; Ho, H.P.; Xu, J.B. High Responsivity, Broadband, and Fast Graphene/Silicon Photodetector in Photoconductor Mode. Adv. Opt. Mater. 2015, 3, 1207–1214. [Google Scholar] [CrossRef]

- Wang, J.; Cheng, Z.; Chen, Z.; Wan, X.; Zhu, B.; Tsang, H.K.; Shu, C.; Xu, J. High-responsivity graphene-on-silicon slot waveguide photodetectors. Nanoscale 2016, 8, 13206–13211. [Google Scholar] [CrossRef] [PubMed]

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Luongo, G.; Giubileo, F.; Genovese, L.; Iemmo, L.; Martucciello, N.; Di Bartolomeo, A. I-V and C-V Characterization of a High-Responsivity Graphene/Silicon Photodiode with Embedded MOS Capacitor. Nanomaterials 2017, 7, 158. https://doi.org/10.3390/nano7070158

Luongo G, Giubileo F, Genovese L, Iemmo L, Martucciello N, Di Bartolomeo A. I-V and C-V Characterization of a High-Responsivity Graphene/Silicon Photodiode with Embedded MOS Capacitor. Nanomaterials. 2017; 7(7):158. https://doi.org/10.3390/nano7070158

Chicago/Turabian StyleLuongo, Giuseppe, Filippo Giubileo, Luca Genovese, Laura Iemmo, Nadia Martucciello, and Antonio Di Bartolomeo. 2017. "I-V and C-V Characterization of a High-Responsivity Graphene/Silicon Photodiode with Embedded MOS Capacitor" Nanomaterials 7, no. 7: 158. https://doi.org/10.3390/nano7070158