International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Index Copernicus Value (2015): 78.96 | Impact Factor (2015): 6.391

# Design and Implementation of Efficient Combinational Logic Circuits with Minimum Area and Circuit Complexity Using Quantum- dot Cellular Automata (QCA)

Zahid Shakeel<sup>1</sup>, Gh Mohammad Wani<sup>2</sup>, Mehboob Ul Amin<sup>3</sup>

<sup>1</sup>Department of Electronics and Communication, Punjab Technicial University Jalander

<sup>2</sup>Department of Physics, S P College Srinagar, India

<sup>3</sup>Department of Electronics and Instrumentation, University of Kashmir

Abstract: Quantum dot cellular automata (QCA), is a rising innovation and a possible alternative for scaling-down trend of VLSI technology. It advantages diminutive size, low power consumption, better switching speed. QCA seems to be a good competitor for future digital systems and widely utilized as a part of advance frameworks. Therefore numerous implementations of QCA based logic functions have been proposed so far. In this paper, an efficient XOR gates is presented. The model proves designing capabilities of combinational logic circuits. The proposed XOR gate has been testified to design logic circuits for QCA. Adder circuit is the most fundamental component used in digital systems. An efficient Half-Adder and Half-Subtractor circuits are designed employing the proposed XOR gate. Performance evolutions of the proposed XOR circuits are compared to its conventional counter parts. The functionality and circuit operation of the proposed designs have been authenticate used QCA Designer simulation tool Ver. 2.0.3.

Keywords: QCA, XOR Gate, Half-Adder, Half-Subtractor, Performance, QCA Designer

#### 1.Introduction

The CMOS technology has been emerged over last four decades as predominant technology of microelectronics industry. It has improved device density, power consumption, and speed of integrated circuits during past several decades by means of reducing the feature size of various semiconducting components. However, CMOS technology has some growing concerns like ultra-thin gate oxides, Offstage leakages and power consumption which cannot be ignored. Today's leading VLSI experts predicts a hard well for CMOS and other conventional fabrication technology in about a decade. This lithographic based technology is now facing serious challenges. Moreover researchers adore more speed and miniaturization has brought them to the verge of classical devices, forcing them to peek in an unknown and astonishing world of nanotechnology and quantum devices. A number of research efforts that have focused on new devices that might replace CMOS technology [1-2]. Utilizing the QCA technology for implementing digital logic circuits is one of the interesting approaches, which seems to be a best competitor and a possible replacement of CMOS technology. QCA nanotechnology is first introduced by Lent et al. [2]; an emerging nanotechnology at the nanotechnology scale by controlling the position of single electron. QCA has achieved significant interest to researchers due to its attractive characteristics such as high device density, low power consumption and small dimensions. It does not involve any voltage or current to encode the information. Position of single electron using Coulombic repellent force has been used to encode the information. Each QCA cells consists of four quantum dots. Two electrons are loaded, in antipodal

sides which determine the logic, "0" and "1". QCA cells are used to implement combinational logic circuits.

Several studies have been reported about QCA circuits [3-15]. Exclusive-OR (XOR) is the most logical gate and is widely used in many combinational and sequential logic circuits. Several XOR gates have been reported in [3-8]. Therefore numerous studies have been reported about QCA Full Adder [9-14] and Programmable Logic Array [16].A new bit serial QCA adder has also been proposed in [17] that uses carry feedback and only requires three majority gates and two inverters.

In this paper a new QCA implementations have been proposed. In the initial step, an efficient two XOR gates with the proper arrangement of QCA cells and clock delays has been proposed. The proposed XOR gates consist of less area and reduced circuit complexity as compared to previous structures. Several conventional XOR designs have been compared to the proposed adder designs in which circuit parameters like area and circuit complexity are in comparison factors. In the next step, the proposed XOR gate has been testified to design a Half-Adder & Half-Subtractor circuit with minimum area and circuit complexity. We aimed to design QCA circuits that are minimal in its use of cell counts, area and clock delays.

Rest the paper is organized in five sections. The second section provides the necessary QCA Materials and Methods. The proposed QCA XOR is presented in third section and is compared with conventional XOR implementations. The proposed 1-bit full Adder (FA) and its simulation results have been discussed in fourth section. Finally, conclude has been discussed in last section.

### 2. Materials and Methods

#### 2.1 QCA cell

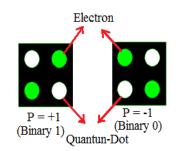

QCA circuits are composed of identical components which are referred to as QCA cells. A QCA cell, a square-shape structure, has four quantum-dots positioned at the four corners and two electrons which are allowed to move between the dots. Due to Coulombic repulsion, the electrons occupy the dots located at the diagonally opposed corners. Hence, two stable states occur which are assigned to logics "0" and "1" [2, 10]. Fig. 1 shows a QCA cell and the two possible polarizations. By placing QCA cells side-by-side, a QCA standard wire can be constructed.

Figure 1: QCA cell and two possible polarizations

#### 2.2 QCA Fundamental Structures

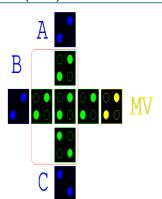

Two basic structures in QCA are Inverter and Majority gate (MG) [10]. Fig. 2 depicts one of the formerly presented Inverters. As illustrated, the input polarization is inversed when it reaches the output cell.

Figure 2: Simple QCA inverter.

In conventional QCA designs, three-input and five-input majority gates play a significant role in general circuit architecture. Therefore, circuit's complexity and latency have been relatively associated to the cells configuration of QCA fundamental gates. Accordingly, various QCA structures for multi-input majority gates have been designed by researchers, so far. Fig. 3 shows layout of a three-input majority gate.

The logic function of MG gate is worked out as: MG (A, B, C) = AB+AC+BC

Figure 3: QCA 3-input Majority gate

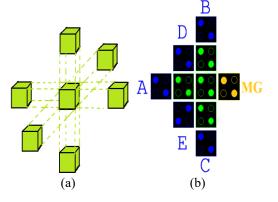

In Fig. 4, two five-input majority gates are displayed which are provided in [18-19]. The output cell of the gate shown in Fig. 4 (a) is a middle cell which is a barrier to cascading gates, however this problem is solved in the design depicted in Fig 4 (b). The logical function of five-input majority gate is written as:

MG(A, B, C, D, E) = ABC + ABD + ABE + ACD + ACE + ADE + BCD + BCE + BDE + CDE

Figure 4: Layouts of two QCA 5-input majority gates (a) in [18] (b) in [19].

# 2.3. Wire Crossing in QCA

Wire crossing is a significant issue in QCA circuit design. Three different crossing methods have been proposed, so far [20]:

- 1)Single-layer crossing: this kind of QCA crossing is implemented in one layer using both 45-degree and 90degree QCA cells, each one dedicated to one side of a crossing. These different cells can pass over the crossing without any significant effect on each other. Fig. 5(a) depicts a single-layer crossing.

- 2)Logical crossing: although this crossing is implemented on a single layer, only one type of QCA cell is required. The effects of wires of a crossing on each other are neutralized utilizing different phases in each wire. Cells with switch and hold phases are allowed to cross over the cells with release and relax phases, respectively. Fig. 5(b) illustrates a QCA logical crossing.

- 3)Multi-layer crossing: unlike the previous one, multi-layer method uses only 45-degree cells or 90-degree ones. One wire of the crossing is transferred to another layer and after passing through the crossing, the wire is returned to the original layer (Fig. 5(c)).

# Volume 6 Issue 1, January 2017

<u>www.ijsr.net</u>

**Figure 5:** Wire crossing methods: (a) Single layer wire crossing (b) Logical crossing (c) Multi-layer wire crossing

## **3.QCA Implementations**

#### 3.1 The Proposed Exclusive-OR (XOR) Gates

In addition to basic and universal logic gates in digital systems, Exclusive-OR (XOR) gate is also widely used for the design of digital circuits. These gates are mainly used in arithmetic operations as well as error detection and correction circuits. XOR gate is usually found as 2-input gates. No multiple-input XOR gates are available since they are complex to fabricate with hardware. Several QCA XOR implementations have been reported in [3-6, 10, 21].

Exclusive-OR (XOR) is a logical operation on two operands that results in a logical value of true if and only if one of the operands, but not both, has a value of true.

The logic expression for XOR gate is:  $A \bigoplus B = A'B + AB'$

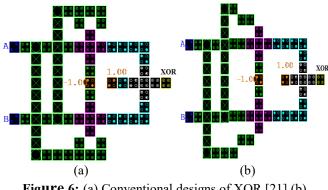

Two such conventional QCA layouts are shown in Fig. 6(a) & (b) [6, 21]. The main drawback of these ciruits are circuit complexity and area. These circuits are constructed using Multi-layer and Wire crossover schemes which causes low robustness and fabrication difficulties in QCA circuits [21-23]. Numerious combinational circuits have been redesigned to reduce the circuit complexity and achieve significent efficiency.

Figure 6: (a) Conventional designs of XOR [21] (b) Conventional designs of XOR [6].

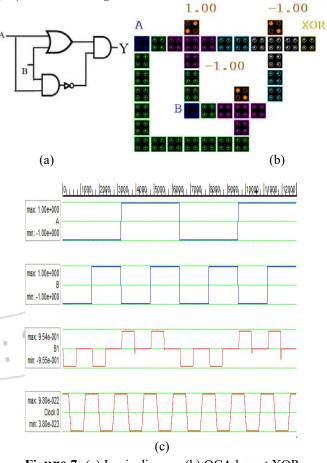

We have proposed an efficient two XOR gates. First one is implemented using Single layer and second layer is implemented using Multilayer. Fig. 7(a) shows the logic diagram of proposed XOR. Single layer is designed using

Volume 6 Issue 1, January 2017 <u>www.ijsr.net</u> Licensed Under Creative Commons Attribution CC BY

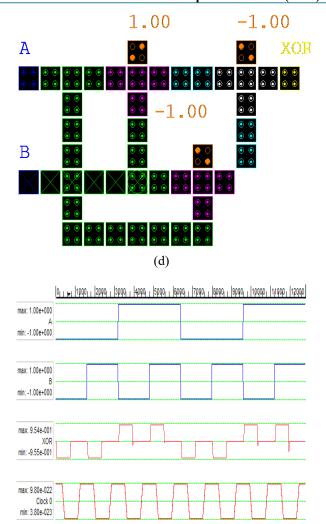

with simple arrangement of standard cells and consist of very less area 0.03um<sup>2</sup>, circuit complexity of 38-cells with proper arrangement of 1-clock delay. The new XOR gate is the modified version of XOR presented in [24]. The results of the comparison of all the existing XOR designs are presented in Table 1. The QCA layout of the modified single layer XOR gate is shown in Fig. 7(d) and simulations results are shown in Fig. 7(c). The second layer is composed of Multi-layer and consists of area 0.04um<sup>2</sup>, circuit complexity of 47-cells with proper arrangement of 1-clock delay. The QCA layout of the Multilayer proposed XOR gate is shown in Fig. 7(d) and simulations results are shown in Fig. 7(d) and simulations results are shown in Fig. 7(d) and simulations results are shown in Fig. 7(e). The proposed layouts can be easily used to design complex circuits based on XOR operation like adder circuits, shift registers etc.

These results indicate that the proposed design consumes smaller area, has less or equal latency and also has less complexity compared to the previous designs except the proposed XOR design in

Figure 7: (a) Logic diagram (b) QCA layout XOR (c)Simulation results

#### International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Index Copernicus Value (2015): 78.96 | Impact Factor (2015): 6.391

(e) Figure 7: (d) QCA layout Multilayer XOR (c)Simulation results

#### 3.2 QCA Layout of Half-Adder

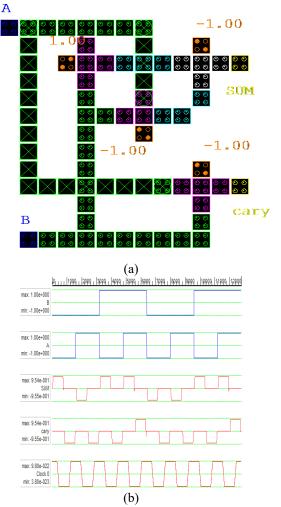

Adder circuits perform various arithmetic operations like addition, subtraction, division and multipulcation; Half-Adder is the main block to design Full Adder. The Halfadder is a performs addition of two bits. It is designed conventionally by XOR and AND gates, with two inputs A and B and output. Sum is produced using XOR gate and Carry is produced using AND gate.

The logic function for Half-adder is: Sum = A'.B + A.B' which is Exclusive-OR (XOR) function Carry = A.B, which is an (AND) function

Fig. 8(a) shows the logic diagram of proposed Half-Adder. It is constructed using Multilayer scheme. The proposed XOR gate present in Fig. 7(d) has been further modified and testified to design Half-Adder. The proposed Half-Adder consists of circuit area of 0.06um<sup>2</sup>, circuit complexity of 82cells with proper arrangement of 1-clock delay. The simulations results of proposed Half-Adder are shown in Fig. 8(b).

Figure 8: (a) QCA layout Half-Adder (b)Simulation results

#### 3.3 QCA Layout of Half-Subtractor

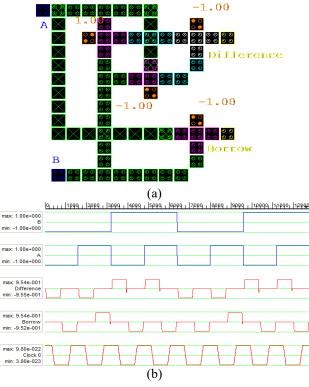

The Half-Subtractor is a combinational circuit that performs subtraction of two bits. It is designed conventionally by XOR, AND and NOT gates. When two inputs A and B are subtracted, the Difference and Borrow outputs are produced. Difference is produced using XOR gate and Borrow is produced using AND gate.

The logic function for Half-Subtractor is: Difference = A'.B + A.B', which is XOR function Borrow = A.B', which is an AND function

Fig. 9(a) shows the logic diagram of proposed Half-Subtractor. The proposed Half-Subtractor consists of circuit area  $0.06 \text{ um}^2$ , circuit complexity of 81-cells with proper arrangement of 1-clock delay. The simulations results of proposed Half-Subtractor are shown in Fig. 9(b).

Figure 8: (a) QCA layout Half-Subtractor (b)Simulation results

## 4. Performance of XOR Gates

Table 1 shows the significant improvements of our proposed designs as compared to [4-5, 6, 10, 21, 24]. Here we have developed an extensive structural analysis in different aspects (Area, Circuit complexity& Clock delays) of full adder structures previously published in literatures. The proposed single layer design is the modified version of previous XOR present in [24]. To correct the circuit functionality we have reduce maximum number of circuit complexity (cell counts) and area in previous XOR presented in [24]. Area and circuit complexity is the major issue for any circuit designers at neno-scale. Therefore in general Table 1 depicts the significent improvements in terms of area and circuit complexity (cell counts) as compared to as compared to conventional counter parts [4-5, 6, 10, 21, 24]. Complexity, area and latency is the major issues for any circuit designers at nano-scale. The proposed XOR implementations are at advantage with the conventional designs and is evident from the said Table.

| Table 1. Comparisons of More Gales |                |                   |               |

|------------------------------------|----------------|-------------------|---------------|

| Feature                            | Complexity     | Area              | Latency       |

|                                    | (No. of cells) | (um <sup>2)</sup> | (clock delay) |

| Ref.(4)                            | 95             | 0.21              | 2.25          |

| Ref.(5)                            | 121            | 0.22              | 1             |

| Ref.(6)                            | 74             | 0.07              | 1             |

| Ref.(10)                           | 84             | 0.08              | 1             |

| Ref.(21)                           | 87             | 0.09              | 1             |

| Ref.(24) Fig 14(b) Previous        | 54             | 0.07              | 1             |

| XOR parameters                     |                |                   |               |

| Single Layer Modified XOR          | 38             | 0.03              | 1             |

| New parameters Fig. 7(b)           |                |                   |               |

| Multiayer Proposed XOR             | 42             | 0.04              | 1             |

| Fig. 7(d)                          |                |                   |               |

Table 1: Comparisons of XOR Gates

# 5. Conclusion

In this paper, two efficient XOR (Single layer & Multilayer) gates have been proposed with the reduced number of circuit complexity (cell counts) and area as compared to conventional counter parts. The comparison of proposed XOR gate has been listed in Table 1. The proposed XOR gates have achieved significant improvements in terms of circuit parameters like area and circuit complexity (cell counts). In addition, the proposed XOR gates have been testified to implement a new Half-Adder and Half-Subtractor circuits for QCA. Bistable approximation simulating engine of QCA Designer tool have been used to verify the operation and simulation results of the proposed circuits.

## References

- R.Compano, L.Molenkamp, D.J.Paul, "Technology roadmap for nano electronics. in: Proceeding of the European Commission IST Programme", Future and Emerging Technologies, Conference 1999.

- [2] C.S.Lent, P.D.Taugaw, W.Porod, and G.H. Berstein, "Quantum Cellular Automata", Nanotechnology, 4, 49, 1993.

- [3] Firdous Ahmad, GM Bhat, "Novel Code Converters Based On Quantum-dot Cellular Automata (QCA)", International Journal of Science and Research (IJSR), 3, 5, 2014.

- [4] S. Roy and B. Saha, "Minority gate oriented logic design with quantum-dot cellular automata", Cellular Automata Lecture Notes in Computer Science, Vol. 4173/2006, 646- 656, Published by Springer, 2006.

- [5] V. C. Teja, S. Polisetti and S. Kasavajjala, "QCA based multiplexing of 16 arithmetic & logical subsystems-a paradigm for nano computing", Proceedings of the 3rd IEEE Int. Conf. on Nano/Micro Engineered and Molecular Systems Jan. 2008.

- [6] S.Karthigai lakshmi, G.Athisha, "Efficient Design of Logical Structures and Functions using Nanotechnology Based Quantum Dot Cellular Automata Design", *International Journal of Computer Applications*, Vol. 3, No.5, pp. 0975 – 8887, June 2010.

- [7] M. Kianpour, R. Sabbaghi-Nadooshan, "Novel Design of n-bit Controllable Inverter by ,Quantum-dot Cellular Automata," Int. J. Nanosci. Nanotechnol., Vol. 10, No. 2, pp. 117-126, June 2014.

- [8] Tantry et al., "Design and Implementation of Multilayer XOR/XNOR Gates Based on Quantum Dot Crllular Automata (QCA)", Journal of Physical Science and International, , 4, 1, 2015.

- [9] Firdous Ahmad, Ghulam Mohiuddin Bhat, Peer Zahoor Ahmad, "Novel Adder Circuits Based on Quantum-Dot Cellular Automata (QCA), Circuits and Systems, 5, 142-152, 2014.

- [10] P. Tougaw and C. Lent, "Logical devices implemented using quantum cellular automata," J. Appl. Phys., Vol. 75, No. 3, pp. 1818–1825, 1994

- [11] W. Wang, K. Walus, and G. Jullien, "Quantum-dot cellular automata adders," In Proceedings of the 2003 3rd IEEE Conference on Nanotechnology, pp. 461–464, 2003

# Volume 6 Issue 1, January 2017

www.ijsr.net

- [12] K Kim, K Wu, R Karri, IEEE Tractions on CAD Integr. Circuits Systems, Vol. 26, PP 176-183, 2007

- [13] R Zhang, K Walus, W Wang, In proceedings of IEEE International Symp. Circuits System, Vol. 3 PP 2522-2526, 2005.

- [14] Santanu Santra, Utpal Roy, "Design and Implementation of Quantum Cellular Automata Based Novel Adder Circuits," World Academy of Science, Engineering, and Technology International Journal of Computer, Information Science and Engineering Vol: 8 No: 1, 2014.

- [15] S.Hu, M. Crocker, M. Niemier, M. Yan, G. Bernstein, "PLAs in quantum-dot cellular automata", Proceeding International Symposim VLSI, pp. 242–247, 2006.

- [16] Fijany, N. Toomarian, K. Modarress, and M. Spotnitz, "Bit-serial adder based on quantum dots," NASA technical report, Jan. 2003.

- [17] M. Rahimi Azghadi, O. Kavehei, K. Navi, "A Novel Design for Quantum-dot Cellular Automata Cells and Full Adders," Journal of Applied Sciences, 7, pp. 3460-3468, 2007.

- [18] K. Navi, R. Farazkish, S. Sayedsalehi, M. Rahimi Azghadi, "A new quantum-dot cellular automata fulladder," Microelectron. J., 41, pp. 820–826. 2010.

- [19] S. Angizi, E. Alkaldy, N. Bagherzadeh, and K. Navi, "Novel Robust Single Layer Wire Crossing Approach for Exclusive OR Sum of Products Logic Design with Quantum-Dot Cellular Automata", Journal of Low Power Electronics, Vol. 10, pp. 259-271, 2014.

- [20] K. Walus and G. Jullien, "Design Tools for an Emerging SoC Technology: Quantum-dot Cellular Automata", *Proc. IEEE*, Vol. 94, No. 6, pp. 1225-1244, June 2006.

- [21] Rajeswari. D, Kolin. Paul and M. Balakrishnan, "Clocking-based Coplanar Wire Crossing Scheme for QCA", 23rd IEEE Int. Conf. VLSI Design, pp. 339-344, 2010.

- [22] S. H. Shin, J. C. Jeon, and K. Y. Yoo, "Design of Wirecrossing Technique based on Difference of Cell State in Quantum-dot Cellular Automata", *International Journal* of Control and Automation, Vol. 7, No. 153, 2014.

- [23] Mohammad Rafiq Beigh, Mohammad Mustafa, Firdous Ahmad, "Performance Evaluation of Efficient XOR Structures in Quantum-Dot Cellular Automata (QCA)", Circuits and Systems, 4, pp. 147-156, 2013.

2319'