Abstract

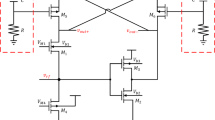

Despite the exceptional progress of MPSoC architectures, on chip communication networks remain a lock for the evolution of their performances due to the power consumption and the delay in data carrying. In this context, the wired radio frequency (RF) network on chip (RFNoC) has emerged. In this paper, we developed a library of RF component models in VHDL-AMS for time domain simulation. This library includes mainly the transmission line (TL) and the RF transceiver components such as the low noise amplifier (LNA), the mixer and the local oscillator (LO). The models consider the conventional parameters describing their performances including the non-linearities, the noise and the bandwidth of the LNA and the mixer. Leakages between ports are also considered for the mixer. The LO model considers the traditional parameters, more importantly its phase noise. The originality of the TL model is the modeling of the skin effect on a wide frequency range for time domain simulations. All the models are validated. Global simulations are performed to demonstrate the interest to accurately model the components of the RFNoC. The developed library is used here for wired RFNoC, however it can be used for all other wired and wireless RF communication system.

Similar content being viewed by others

References

Pavlidis, V. F., & Friedman, E. G. (2007). 3-D topologies for networks-on-chip. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 15(10), 1081–1090.

Kurian, G., Miller, J. E., Psota, J., Eastep, J., Liu, J., Michel, J., et al. (2010). ATAC: A 1000-core cache-coherent processor with on-chip optical network. In Proceedings of the 19th international conference on parallel architectures and compilation techniques (pp. 477–488). New York, NY: ACM.

Shacham, A., Bergman, K., & Carloni, L. P. (2008). Photonic networks-on-chip for future generations of chip multiprocessors. IEEE Transactions on Computers, 57(9), 1246–1260.

Vantrease, D., Schreiber, R., Monchiero, M., McLaren, M., Jouppi, N. P., Fiorentino, M., et al. (2008). Corona: System implications of emerging nanophotonic technology. SIGARCH Computer Architecture News, 36(3), 153–164.

Chang, M. F., Cong, J., Kaplan, A., Naik, M., Reinman, G., Socher, E., et al. (2008). CMP network-on-chip overlaid with multi-band RF-interconnect. In IEEE 14th international symposium on high performance computer architecture, 2008. HPCA 2008 (pp. 191–202).

Chang, M.-C. F., Roychowdhury, V. P., Zhang, L., Shin, H., & Qian, Y. (2001). RF/wireless interconnect for inter- and intra-chip communications. Proceedings of the IEEE, 89(4), 456–466.

Ganguly, A., Chang, K., Deb, S., Pande, P. P., Belzer, B., & Teuscher, C. (2011). Scalable hybrid wireless network-on-chip architectures for multicore systems. IEEE Transactions on Computers, 60(10), 1485–1502.

Rebeiz, E., & Cabric, D. (2013). How wideband receiver nonlinearities impact spectrum sensing. In Global conference on signal and information processing (GlobalSIP), 2013 IEEE (pp. 1178–1181).

IEEE-std. (2007). IEEE standard VHDL analog and mixed-signal extensions. IEEE Std. 1076.1-2007 (Revision of IEEE Std 1076.1-1999) (pp. c1–328).

Winter, M., Prusseit, S., & Gerhard, P. F. (2010). Hierarchical routing architectures in clustered 2D-mesh networks-on-chip. In 2010 international SoC design conference (ISOCC) (pp. 388–391).

Tam, S. W., & Chang, M.-C. F. (2011). RF/wireless-interconnect: The next wave of connectivity. Science China Information Sciences, 54(5), 1026–1038.

Drillet, F., Hamieh, M., Zerioul, L., Briere, A., Unlu, E., Ariaudo, M., et al. (2014). Flexible radio interface for NOC RF-interconnect. In 2014 17th Euromicro conference on digital system design (DSD) (pp. 36–41).

Unlu, E., Hamieh, M., Moy, C., Ariaudo, M., Louet, Y., Drillet, F., et al. (2014). An OFDMA based RF interconnect for massive multi-core processors. In 2014 eighth IEEE/ACM international symposium on networks-on-chip (NoCS) (pp. 182–183).

Chang, M. C. F., Cong, J., Kaplan, A., Naik, M., Reinman, G., Socher, E., et al. (2012). On-chip radio frequency (RF) interconnects for network-on-chip designs. Google Patents. US Patent 8,270,316.

Tam, S.-W., Socher, E., Wong, A., & Chang, M. C. F. (2009). A simultaneous tri-band on-chip RF-interconnect for future network-on-chip. In 2009 symposium on VLSI circuits (pp. 90–91).

Carpenter, A., Hu, J., Kocabas, O., Huang, M., & Wu, H. (2012). Enhancing effective throughput for transmission line-based bus. In 2012 39th annual international symposium on computer architecture (ISCA) (pp. 165–176).

Dokhanchi, A., Jahanian, A., Mehrshahi, E., & Teimoori, M. T. (2011). Feasibility study of using the RF interconnects in large FPGAS to improve routing tracks usage. In 2011 IEEE computer society annual symposium on VLSI (ISVLSI) (pp. 1–6).

Karkar, A., Mak, T., Tong, K. F., & Yakovlev, A. (2016). A survey of emerging interconnects for on-chip efficient multicast and broadcast in many-cores. IEEE Circuits and Systems Magazine, 16(1), 58–72.

Das, R., Narayanasamy, S., Satpathy, S. K., & Dreslinski, R. G. (2013). Catnap: Energy proportional multiple network-on-chip. SIGARCH Computer Architecture News, 41(3), 320–331.

Li, H., & Miao, C. (2005). Behavioral modeling and simulation of RF LNA with VHDL-AMS. Proceedings of SPIE, 6035, 60351H-60351H-9.

Yang, W., Carter, H., & Yan, J. (2004). A high-level VHDL-AMS model design methodology for analog RF LNA and mixer. In Proceedings of the 2004 IEEE international behavioral modeling and simulation conference, 2004. BMAS 2004 (pp. 125–129).

Nicolle, B., Tatinian, W., Jacquemod, G., Mayol, J.-J., & Oudinot, J. (2007). RF library based on block diagram and behavioral descriptions. In IEEE International behavioral modeling and simulation workshop, 2007. BMAS 2007 (pp. 52–57).

David, J. B. (2010). Radio receiver mixer model for event-driven simulators to support functional verification of RF-SOC wireless links. In 2010 IEEE international behavioral modeling and simulation conference (BMAS) (pp. 42–47).

Joannon, Y., Beroulle, V., Khouri, R., Robach, C., Tedjini, S., & Carbonero, J.-L. (2006). Behavioral modeling of WCDMA transceiver with VHDL-AMS language. In 2006 IEEE design and diagnostics of electronic circuits and systems (pp. 111–116).

Mentor. (2009) ADMS RF components library, mentor graphics.

Normark, E., Yang, L., Wakayama, C., Nikitin, P., & Shi, R. (2004). VHDL-AMS behavioral modeling and simulation of a pi;/4 DQPSK transceiver system. In Proceedings of the 2004 IEEE international behavioral modeling and simulation conference, 2004. BMAS 2004 (pp. 119–124).

Box, G. E. P., & Muller, M. E. (1958). A note on the generation of random normal deviates. The Annals of Mathematical Statistics, 29(2), 610–611.

Gautier, J.-L., Quintanel, S., Ariaudo, M., & Duperrier, C. (2014). Design of microwave active devices. Hoboken: ISTE Wiley.

Razavi, B. (1998). RF microelectronics. Upper Saddle River: Prentice-Hall.

Staszewski, R. B., Fernando, C., & Balsara, P. T. (2005). Event-driven simulation and modeling of phase noise of an rf oscillator. IEEE Transactions on Circuits and Systems I: Regular Papers, 52(4), 723–733.

Tran, L. N., Pasquet, D., Bourdel, E., & Quintanel, S. (2008). Cad-oriented model of a coplanar line on a silicon substrate including eddy-current effects and skin effect. IEEE Transactions on Microwave Theory and Techniques, 56(3), 663–670.

Xu, J.-F., & Yan, N. (2011). Analysis and simulation for RF interconnect. In Progree In electromagnetics research symposium (pp. 1410–1414).

Zerioul, L., Ariaudo, M., & Bourdel, E. (2015). Optimization of spectral resources allocation in a context of RF network on chip. In 2015 IEEE 13th international new circuits and systems conference (NEWCAS) (pp. 1–4).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Zerioul, L., Ariaudo, M. & Bourdel, E. RF transceiver and transmission line behavioral modeling in VHDL-AMS for wired RFNoC. Analog Integr Circ Sig Process 92, 103–114 (2017). https://doi.org/10.1007/s10470-017-0975-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-017-0975-6