Abstract

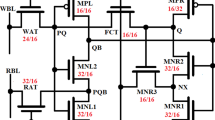

Static random access memory (SRAM) cell design has undergone extensive development to achieve good performance and low power consumption. This paper introduces an SRAM cell with ten carbon nanotube field effect transistors (CNTFETs) named 10 T CNTFET SRAM cell to help with that and to address the drawback of most SRAM cells caused by their poor stability during read operation. The Schmitt-trigger (ST)-based inverter and PPN-inverter are coupled back to back to create the novel SRAM cell structure. Additionally, single-ended writing, feed-back cutting, and single-ended reading are used in this novel SRAM cell. The single-ended writing technique and feed-back cutting method are used to their full potential to increase the write static noise margin (WSNM) of this 10 T CNTFET SRAM cell. The single-ended read mode of this 10 T CNTFET SRAM cell increases the read static noise margin (RSNM) as the storage nodes are not disturbed. The hold power, read power, WSNM, hold static noise margin (HSNM), RSNM, read delay, leakage power, and VDDmin of this 10 T CNTFET SRAM cell are 0.5527 nW, 1.8087 nW, 432.4 mV, 360 mV, 360 mV, 5.0651 pS, 0.276 nW, and 32.1 mV, respectively. To understand the performance of this introduced SRAM cell and several existing SRAM cells are simulated and the parameters are compared. A comparative study shows that the introduced cell is more stable than the other cells while consuming less power during reading and holding. Furthermore, the new cell reads much faster and has less VDDmin than the other bit cells. This research also documents how SRAM cell performance changes when the CNTFET parameters change. Using the 32 nm CNTFET model from Stanford University using the Hewlett simulation program with integrated circuit emphasis (HSPICE) simulation tool, the simulation is carried out.

Similar content being viewed by others

Data Availability

The data will be shared on request by the corresponding author.

References

E. Abbasian, M. Gholipour, Design of a highly stable and robust 10T SRAM cell for low-power portable applications. Circuits Syst. Signal Process 41, 5914–5932 (2022)

E. Abbasian, M. Gholipour, Design of a Schmitt-Trigger-based 7T SRAM cell for variation resilient low–energy consumption and reliable internet of things applications. AEU Int. J. Electron. Commun. 138, 153899 (2021)

E. Abbasian, Design and investigation of stability- and power-improved 11T SRAM cell for low-power devices. Int J Circ Theor Appl. 50, 3827–3845 (2022)

E. Abbasian, E. Mani, M. Gholipour, A schmitt-trigger-based low-voltage 11 T SRAM cell for low-leakage in 7-nm FinFET technology. Circuits Syst. Signal Process. 41, 3081–3105 (2022)

E. Abbasian, F. Izadinasab, M. Gholipour, A reliable low standby power 10T SRAM cell with expanded static noise margins. IEEE Trans. Circuits Syst. I Regul. 69, 1606–1616 (2022)

E. Abbasian, S. Birla, M. Gholipour, Ultra-low-power and stable 10-nm FinFET 10T sub-threshold SRAM. Microelectron. J. 123, 105427 (2022)

S. Ahmad, B. Iqbal, N. Alam, M. Hasan, Low leakage fully half-select-free robust sRAM cells with BTI reliability analysis. IEEE Trans. Device Mater. Reliab. 18, 337–349 (2018)

Akutagawa, M., Emoto, T., Garrigues, L., Boeuf, P. (2022) Design and performance improvement of 10T SRAM using sleepy keeper and drain gating techniques. Ranu Chaurasia et al 2022 IOP Conf. Ser.: Mater. Sci. Eng. 1272: 012007.

P. Avula, Improvement of SRAM stability using read and write assist techniques. Int. J. Eng. Technol. 6, 78–82 (2017)

S. Bala, M. Khosla, Design and analysis of electrostatic doped tunnel CNTFET for various process parameters variation. Superlattices Microstruct. 124, 160–167 (2018)

D. Bosch, Novel fine-grain back-bias assist techniques for 3D-monolithic 14 nm FDSOI top-tier SRAMs. Solid State Electron. 168, 107720 (2020)

K. Cho, J. Park, T.W. Oh, S.O. Jung, One-sided schmitt-trigger-based 9T SRAM cell for near-threshold operation. IEEE Trans. Circuits Syst. I Regul. Pap. 67(5), 1551–61 (2020)

C. Duari, S. Birla, Low leakage SRAM cell with improved stability for IoT applications birla stability for IoT low leakage SRAM cell. Procedia Comput. Sci. 171, 1469–1478 (2020)

M. Elangovan, K. Gunavathi, High stability and low-power dual supply-stacked CNTFET SRAM cell. Innov. Electron. Commun. Eng. 33, 205–210 (2019)

M. Elangovan, K. Gunavathi, High stable and low power 10T CNTFET SRAM cell. J. Circuits Syst. Comput. 29(10), 2050158 (2020)

Elangovan, M., Gunavathi, K. (2018) Stability analysis of 6T CNTFET SRAM cell for single and multiple CNTs. In: 2018 4th International conference on devices, circuits and systems (ICDCS), Coimbatore, India. 63–67.

M. Elangovan, D. Karthickeyan, M. Arul Kumar, R. Ranjith, Darlington based 8T CNTFET SRAM cells with low power and enhanced write stability. Trans. Electr. Electron. Mater. 23, 122–135 (2022)

M. Elangovan, M. Muthukrishnan, Design of high stability and low power 7T SRAM cell in 32-NM CNTFET technology. J. Circuits Syst. Comput. 31(13), 2250233 (2022)

M. Elangovan, R. Ranjith, S. Devika, PDP Analysis of CNTFET Full Adders for Single and Multiple Threshold Voltages. Advances in VLSI, Communication, and Signal Processing. Lecture Notes in Electrical Engineering. 683. 2021

M. Elangovan, A novel darlington-based 8T CNTFET SRAM cell for low power applications. J. Circuits, Syst. Comput. 30(12), 2150213 (2021)

S.S. Ensan, M. Hossein, M. Behzad, E. Shaahin, H. Ali, A. Kusha, A low - leakage and high - writable SRAM cell with back - gate biasing in FinFET technology. J. Comput. Electron. 18, 519–526 (2019)

M. Khaleqi, Q. Jooq, A. Mir, S. Mirzakuchaki, A. Farmani, A robust and energy-efficient near-threshold SRAM cell utilizing ballistic carbon nanotube wrap-gate transistors. AEUE - Int. J. Electron. Commun. 110, 152874 (2019)

R. Krishna, P. Duraiswamy, A technique of designing low leakage SRAM in deep sub-micron technology. in: 2020 IEEE International Conference of Electronics and Computing and Communication Technolgies pp. 1–5, 2020

A. Kumar, S. Sharma, N. Goyal, A. Singh, X. Cheng, P. Singh, Secure and energy-efficient smart building architecture with emerging technology IoT. Comput. Commun. 176, 207–217 (2021)

G.S. Kumar, A. Singh, B. Raj, Design and analysis of a gate-all-around CNTFET-based SRAM cell. J. Comput. Electron. 17, 138–145 (2017)

M. Kumar, Dynamic power dissipation analysis in CMOS VLSI circuit design with scaling down in technology. J. Act. Passiv. Electron. Devices. 12, 55–61 (2020)

E. Mani, E. Abbasian, M. Gunasegeran, S. Sofimowloodi, Design of high stability, low power and high speed 12 T SRAM cell in 32-nm CNTFET technology. AEU - Int. J. Electron. Commun. 154, 154308 (2022)

D. Nayak, D.P. Acharya, P.K. Rout, U. Nanda, A novel charge recycle read write assist technique for energy efficient and fast 20 nm 8T-SRAM array. Solid State Electron. 148, 43–50 (2018)

N. K. Niranjan, Parametric analysis of a hybrid 1-bit full adder in UDSM and CNTFET Technology. in: 2016 International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), Chennai, India, 2016, 4267–4272

M. Nizamuddin, H. Shakir, P. Gupta, Design of ambipolar CNTFET based universal logic gates. in: 2019 International Conference on Power Electronics, Control and Automation (ICPECA) 2019 Nov 16 (pp. 1-5). IEEE

S. Pal, S. Bose, W.H. Ki, A. Islam, Half-select-free low-power dynamic loop-cutting write assist SRAM cell for space applications. IEEE Trans. Electron Devices 67, 80–89 (2020)

P.K. Patel, M.M. Malik, T.K. Gupta, Reliable high-yield CNTFET-based 9T SRAM operating near threshold region. J. Comput. Electron. 17, 774–783 (2018)

S. Rani, S.H. Ahmed, R. Rastogi, Dynamic clustering approach based on wireless sensor networks genetic algorithm for IoT applications. Wireless Netw. 26, 2307–2316 (2020)

A. Sachdeva, L. Gupta, K. Sharma, M. Elangovan, A CNTFET based bit-line powered stable SRAM design for low power applications. ECS J. Solid State Sci. Technol. 12, 041006 (2023)

A. Sachdeva, V.K. Tomar, A soft-error resilient low power static random access memory cell. Analog Integr. Circuits Signal Process. 109, 187–211 (2021)

R. Sahoo, S. K. Sahoo, K. C. Sankisa, Design of an efficient CNTFET using optimum number of CNT in channel region for logic gate implementation, in: International Conference on VLSI Systems, Architecture, Technology and Applications (VLSI-SATA), 2015, pp. 1–4

V. Srinivasan, R.V. Venkatraman, K.K. Senthil, Schmitt trigger based SRAM cell for ultralow power operation- a CNFET based approach. Procedia Eng. 64, 115–124 (2013)

D. Tripathy, T. Manasneha, V. Das, A single-ended TG based 8T SRAM cell with increased data stability and less delay. Electron. Inf. Commun. Technol. Proc. 2018, 1282–1285 (2017)

S. Vats, R.K. Chauhan, A novel technique to reduce write delay of SRAM architectures. WSEAS Trans. Circuits Syst. 10(12), 403–12 (2011)

A.S. Vidhyadharan, S. Vidhyadharan, A novel ultra-low-power CNTFET and 45 nm CMOS based ternary SRAM. Microelectron. J. 111, 105033 (2021)

N. Yadav, A.P. Shah, S.K. Vishvakarma, Stable, reliable, and bit-interleaving 12T SRAM for space applications: a device circuit co-design. IEEE Trans. Semicond. Manuf. 30, 276–284 (2017)

Z. Zhang, J. G. Delgado-Frias, CNTFET 8T SRAM cell performance with near-threshold power supply scaling. in: 2013 IEEE International Symposium on Circuits and Systems (ISCAS) 2013 May 19 (pp. 2123-2126). IEEE

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interests

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper. Authors confirm that they have no conflict of interest as well as no financial interests related to work submitted for possible publication in this Journal. The data generated and analyzed during this study are available from the corresponding author upon reasonable request.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Elangovan, M., Sharma, K., Sachdeva, A. et al. Read Improved and Low Leakage Power CNTFET Based Hybrid 10t SRAM Cell for Low Power Applications. Circuits Syst Signal Process 43, 1627–1660 (2024). https://doi.org/10.1007/s00034-023-02529-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-023-02529-6