Abstract

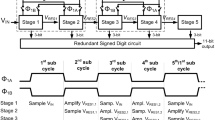

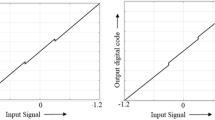

This chapter presents a high-speed simulation tool for the design and analysis of pipelined analog-to-digital converters (ADCs) implemented using the Python programming language. The development of an ADC simulator requires the behavior modeling of the basic building blocks and their possible interconnections to form the final converter. This chapter presents a pipeline ADC simulator tool that allows topology selection and digital calibration of the frontend blocks. Several block nonlinearities are included in the simulation, such as thermal noise, capacitor mismatch, gain and offset errors, parasitic capacitances, settling errors, and other error sources.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Vital, J., Franca, J.: Synthesis of high-speed A/D converter architectures with flexible functional simulation capabilities. In: Proceedings of IEEE International Symposium on Circuits and Systems, pp. 2156–2159 (1992)

Malcovati, P. et al.: Behavioral modeling of switched-capacitor sigma-delta modulators. In: IEEE Transactions on Circuits and Systems I, Fundamental Theory and Applications, vol. 50, pp. 352–364 (2003)

Zare-Hoseini, H., Kale, I., Shoaei, O.: Modeling of switched-capacitor delta-sigma modulators in SIMULINK. IEEE Trans. Instrum. Meas. 54, 1646–1654 (2005)

Hamoui, A.A., Alhajj, T., Taherzadeh-Sani, M.: Behavioral modeling of opamp gain and dynamic effects for power optimization of delta-sigma modulators and pipelined ADCs. In: Proceedings of International Symposium on Low Power Electronics and Design (ISLPED), pp. 330–333 (2006)

Medeiro, F., Pérez-Verdú, B., Rodríguez-Vázquez, A., Huertas, J.L.: A vertically integrated tool for automated design of sigma delta modulators. IEEE J. Solid-State Circuits 30, 762–772 (1995)

Goes, J., Vital, J.C., Franca, J.E.: Systematic design for optimization of high-speed self-calibrated pipelined A/D converters. IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process 45, 1513–1526 (1998)

Horta, N., Franca, J.: Algorithm-Driven Synthesis of Data Conversion Architectures. IEEE Trans. Comput. Aided Des 16(10), 1116–1135 (1997)

Horta, N., Franca, J., Leme, C.: Framework for architecture synthesis of data conversion systems employing binary-weighted capacitor arrays. In: Proceedings of IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1789–1782 (1991)

Guilherme, J., Horta, N., Franca, J.: Symbolic synthesis of non-linear data converters. In: Proceedings of IEEE International Conference on Electronics Circuits and Systems (ICECS), vol. 3, pp. 219–222 (1998)

Vital, J., Horta, N., Silva, N., Franca, J.: CATALYST: a highly flexible CAD tool for architecture-level design and analysis of data converters. In: Proceedings of Joint Conference European Design Automation Conference and European Application Specific Integrated Circuit (EDAC-EUROASIC), pp. 472–477 (1993)

Horta, N., Fino, M., Goes, J.: Symbolic techniques applied to switched-current ADCs synthesis. In: Proceedings of IEEE International Symposium on Circuits and Systems (ISCAS), Geneva, Switzerland, pp, 129–132 (2000)

Ruiz-Amaya, J. et al.: High-level synthesis of switched-capacitor, switched-current and continuous-time sigma-delta modulators using Simulink based time-domain behavioral models. IEEE Trans. Circuit Syst. I, Reg. Papers, vol. 52, pp. 1795–1810 (2005)

Bilhan, E. et al.: Behavioral model of pipeline ADC by using SIMULINK. In: Proceedings of Southwest Symposium Mixed-Signal Design, pp. 147–151 (2001)

Phelps, R. et al. Anaconda: simulation-based synthesis of analog circuits via stochastic pattern search. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 19, 703–717 (2000)

Ochotta, E., Carley, R.L.: Synthesis of high-performance analog circuits in ASTRX/OBLX. IEEE Trans Comput. Aided Des. Integr. Circuits Syst. 15(3), 273–294 (1996)

Kwok, P.T.M., Luong, H.C.: Power optimization for pipeline analog-to-digital converters. IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process. 46, 549–553 (1999)

Silva, C., Ayzac, P., Guilherme, J., Horta, N.: SCALES—A behavioral simulator for pipelined analog-to-digital converter design. In: International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design—SMAC, pp. 149–152 (2012)

Lee, S.H., Song, B.S.: Digital-domain calibration of multistep analog-to-digital converters. IEEE JSSC 27(12), 1679–1688 (1992)

James, C.: Clocking high-speed A/D converters. National Semiconductors, App. Note 1558 (2007)

Andrea, B.: Analog-to-digital data converters. Universitá degli Studi di Lecce. Lecture presentation, pp. 1–322 (2007)

Mikael, G., Jacob, W., Nianxiong, T.: CMOS Data Converters for Communications, pp. 229–256. Kluwer Academic Publishers, NY (2002) (ISBN 0-306-47305-4)

Cline, David, Gray, Paul: A power optimized 13-bit 5 Msamples/s pipelined analog to digital converter in 1.2 μm CMOS. IEEE J. Solid State Circuits 30(4), 443–452 (1995)

Zanchi, A., Tsay, F., Papantonopoulos, I.: Impact of capacitor dielectric relaxation on a 14-bit 70MS/s pipeline ADC in 3 V BiCMOS. IEEE J. Solid-State Circuits 38(12), 2077–2086 (2003)

Doernberg, J., Lee, H.S., Hodges, D.A.: Full-speed testing of A/D converters. IEEE J. Solid-State Circuits, SC-19(6), 820–827 (1984)

Schiff, M.: Spectrum analysis using digital FFT techniques. Agilent Technologies. AN106A (1997)

Sahoo, B.D., Razavi, B.: A fast simulator for pipelined A/D converters. In: IEEE Circuits Syst. MWSCAS ’09. (2), 402–406 (2009)

Navin, V., Hassoun, M., Ray, T., Marwan; Black, W., Lee, E., Soenen, E., Geiger, R.: A simulation environment for pipelined analog-to-digital converters. In: IEEE International Symposium on Circuits and Systems, pp. 1620–1623, 9–12 June 1997

Zareba, G., Palusinski, O.: Behavioral simulator of analog-to-digital converters for telecommunication applications. In: Behavioral Modeling and Simulation Conference BMAS 2004, University of Arizona, pp. 1–6 (2004)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2015 Springer International Publishing Switzerland

About this chapter

Cite this chapter

Silva, C., Ayzac, P., Horta, N., Guilherme, J. (2015). Nonlinearities Behavioral Modeling and Analysis of Pipelined ADC Building Blocks. In: Fakhfakh, M., Tlelo-Cuautle, E., Siarry, P. (eds) Computational Intelligence in Analog and Mixed-Signal (AMS) and Radio-Frequency (RF) Circuit Design. Springer, Cham. https://doi.org/10.1007/978-3-319-19872-9_8

Download citation

DOI: https://doi.org/10.1007/978-3-319-19872-9_8

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-19871-2

Online ISBN: 978-3-319-19872-9

eBook Packages: Computer ScienceComputer Science (R0)