Abstract

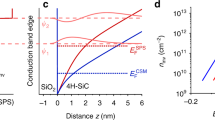

High density of interface traps at the SiC-SiO2 interface gives rise to lower mobilities and currents in SiC MOSFETs. Detailed investigations are performed to measure and characterize these interface traps using experimental and modeling methods [1–3]. Recent measurements of threshold voltage instabilities by fast I–V methods have shown that the SiC-SiO2 interface not only contains fast interface traps, but also slower near-interface and oxide traps [4, 5]. Steady state modeling and simulations cannot characterize the effects of each of these defects. We have hence developed a detailed time dependent modeling scheme for dynamic interface trap occupation, and incorporated it into our 2D transient device simulator. We use the transient modeling to separate out and individually characterize interface, near-interface and oxide traps in 4H-SiC MOS devices.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

N.S. Saks, et. al., App. Phys Lett, 80, 3219 (2002)

E. Pippel, et. al., JAP 97, 034302 (2005)

S. Potbhare, et. al., JAP 100, 044515 (2006)

A. Lelis, et. al., Mat. Sci. Forum Vols. 527–529, p. 1317 (2006)

M. Gurfinkel, et. al., IEEE HRW 2006, 49 (2006)

W. Shockley and W. T. Read Jr., Phys. Rev., 87, 835 (1952)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2007 Springer-Verlag Wien

About this paper

Cite this paper

Potbharel, S., Goldsman, N., Pennington, G., Akturk, A., Lelis, A. (2007). Transient Characterization of Interface Traps in 4H-SiC MOSFETs. In: Grasser, T., Selberherr, S. (eds) Simulation of Semiconductor Processes and Devices 2007. Springer, Vienna. https://doi.org/10.1007/978-3-211-72861-1_42

Download citation

DOI: https://doi.org/10.1007/978-3-211-72861-1_42

Publisher Name: Springer, Vienna

Print ISBN: 978-3-211-72860-4

Online ISBN: 978-3-211-72861-1

eBook Packages: EngineeringEngineering (R0)