Abstract

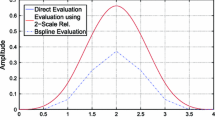

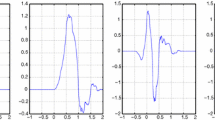

Based on B-spline factorization, a new category of architectures for Discrete Wavelet Transform (DWT) is proposed in this paper. The B-spline factorization mainly consists of the B-spline part and the distributed part. The former is proposed to be constructed by use of the direct implementation or Pascal implementation. And the latter is the part introducing multipliers and can be implemented with the Type-I or Type-II polyphase decomposition. Since the degree of the distributed part is usually designed as small as possible, the proposed architectures could use fewer multipliers than previous arts, but more adders would be required. However, many adders can be implemented with smaller area and lower speed because only few adders are on the critical path. Three case studies, including the JPEG2000 default (9, 7) filter, the (6, 10) filter, and the (10, 18) filter, are given to demonstrate the efficiency of the proposed architectures.

Similar content being viewed by others

References

D. Taubman, “Successive Refinement of Video: Fundamental Issues, Past Efforts and New Directions,” in International Symposium on Visual Communications and Image Processing, 2003.

K.K. Parhi and T. Nishitani, “VLSI Architectures for Discrete Wavelet Transforms,” IEEE Transactions on Very Large Scale Integration Systems, vol. 1, no. 2, pp. 191–202, 1993.

M. Vishwanath, R.M. Owens, and M.J. Irwin, “VLSI Architectures for the Discrete Wavelet Transform,” IEEE Transactions on Circuis and Systems-II: Analog and Digital Signal Processing, vol. 42, no. 5, 1995, pp. 305–316.

C. Chakrabarti, M. Vishwanath, and R.M. Owens, “Architectures for Wavelet Transforms: A Survey,” Journal of VLSI Signal Processing, vol. 14, 1996, pp. 171–192.

K. Andra, C. Chakrabarti, and T. Acharya, “A VLSI Architecture for Lifting-Based Forward and Inverse Wavelet Transform,” IEEE Transactions on Signal Processing, vol. 50, no. 4, 2002, pp. 966–977.

W. Jiang and A. Ortega, “Lifting Factorization-Based Discrete Wavelet Transform Architecture Design,” IEEE Transactions on Circuits and Systems for Video Technology, vol. 11, no. 5, 2001, pp. 651–657.

C.-T. Huang, P.-C. Tseng, and L.-G. Chen, “Flipping Structure: An Efficient VLSI Architecture for Lifting-Based Discrete Wavelet Transform,” IEEE Transactions on Signal Processing, vol. 52, no. 4, 2004, pp. 1080–1089.

P.P. Vaidyanathan, Multirate Systems and Filter Banks, Prentice Hall, 1993.

K.K. Parhi, VLSI Digital Signal Processing Systems: Design and Implementation, John Wiley & Sons, 1999.

W. Sweldens, “The Lifting Scheme: A Custom-Design Construction of Biorthogonal Wavelets,” Applied and Computaional Harmonic Analysis, vol. 3, no. 15, 1996, pp. 186–200.

I. Daubechies and W. Sweldens, “Factoring Wavelet Transforms Into Lifting Steps,” The Journal of Fourier Analysis and Applications, vol. 4, 1998, pp. 247–269.

M. Unser and T. Blu, “Wavelet Theory Demystified,” IEEE Transactions on Signal Processing, vol. 51, no. 2, 2003, pp. 470–483.

M.J. Tsai, J.D. Villasenor, and F. Chen, “Stack-Run Image Coding,” IEEE Transactions on Circuits and Systems for Video Technology, vol. 6, no. 5, 1996, pp. 519–521.

S.G. Mallat, “A Theory for Multiresolution Signal Decomposition: The Wavelet Representation,” IEEE Transactions on Pattern Analysis and Machine Intelligence, vol. 11, no. 7, 1989, pp. 674–693.

S. Mallat, A Wavelet Tour of Signal Processing, Academic Press, 1998.

N. Polyak and W.A. Pearlman, “A New Flexible Bi-Orthogonal Filter Design for Multiresolution Filterbanks with Application to Image Compression,” IEEE Transactions on Signal Processing, vol. 48, no. 8, 2000, pp. 2279–2288.

Author information

Authors and Affiliations

Corresponding author

Additional information

Chao-Tsung Huang was born in Kaohsiung, Taiwan, R.O.C., in 1979. He received the B.S. degree from the Department of Electrical Engineering, National Taiwan University, Taipei, Taiwan, R.O.C., in 2001. He currently is working toward the Ph.D. degree at the Graduate Institute of Electronics Engineering, National Taiwan University. His major research interests include VLSI design and implementation for signal processing systems.

Po-Chih Tseng was born in Tao-Yuan, Taiwan in 1977. He received the B.S. degree in Electrical and Control Engineering from National Chiao Tung University in 1999 and the M.S. degree in Electrical Engineering from National Taiwan University in 2001. He currently is pursuing the Ph.D. degree at the Graduate Institute of Electronics Engineering, Department of Electrical Engineering, National Taiwan University. His research interests include VLSI design and implementation for signal processing systems, energy-efficient reconfigurable computing for multimedia systems, and power-aware image and video coding systems.

Liang-Gee Chen received the B.S., M.S., and Ph.D. degrees in electrical engineering from National Cheng Kung University, Tainan, Taiwan, R.O.C., in 1979, 1981, and 1986, respectively.

In 1988, he joined the Department of Electrical Engineering, National Taiwan University, Taipei, Taiwan, R.O.C. During 1993–1994, he was a Visiting Consultant in the DSP Research Department, AT&T Bell Labs, Murray Hill, NJ. In 1997, he was a Visiting Scholar of the Department of Electrical Engineering, University of Washington, Seattle. Currently, he is Professor at National Taiwan University, Taipei, Taiwan, R.O.C. His current research interests are DSP architecture design, video processor design, and video coding systems.

Dr. Chen has served as an Associate Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY since 1996, as Associate Editor of the IEEE TRANSACTIONS ON VLSI SYSTEMS since 1999, and as Associate Editor of IEEE TRANSACTIONS CIRCUITS AND SYSTEMS II since 2000. He has been the Associate Editor of the Journal of Circuits, Systems, and Signal Processing since 1999, and a Guest Editor for the Journal of Video Signal Processing Systems. He is also the Associate Editor of the PROCEEDINGS OF THE IEEE. He was the General Chairman of the 7th VLSI Design/CAD Symposium in 1995 and of the 1999 IEEE Workshop on Signal Processing Systems: Design and Implementation. He is the Past-Chair of Taipei Chapter of IEEE Circuits and Systems (CAS) Society, and is a member of the IEEE CAS Technical Committee of VLSI Systems and Applications, the Technical Committee of Visual Signal Processing and Communications, and the IEEE Signal Processing Technical Committee of Design and Implementation of SP Systems. He is the Chair-Elect of the IEEE CAS Technical Committee on Multimedia Systems and Applications, During 2001-2002, he served as a Distinguished Lecturer of the IEEE CAS Society. He received the Best Paper Award from the R.O.C. Computer Society in 1990 and 1994. Annually from 1991 to 1999, he received Long-Term (Acer) Paper Awards. In 1992, he received the Best Paper Award of the 1992 Asia-Pacific Conference on circuits and systems in the VLSI design track. In 1993, he received the Annual Paper Award of the Chinese Engineer Society. In 1996 and 2000, he received the Outstanding Research Award from the National Science Council, and in 2000, the Dragon Excellence Award from Acer. He is a member of Phi Tan Phi.

Rights and permissions

About this article

Cite this article

Huang, CT., Tseng, PC. & Chen, LG. VLSI Architecture for Forward Discrete Wavelet Transform Based on B-spline Factorization. J VLSI Sign Process Syst Sign Image Video Technol 40, 343–353 (2005). https://doi.org/10.1007/s11265-005-5269-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-005-5269-z