Abstract

The hybrid halide perovskites combine the low-cost processing characteristics of organic materials with the performance factors of inorganic compounds. Recently the power conversion efficiencies of perovskite photovoltaic solar cells have reached a respective value of ∼20%. The charge transport properties were indirectly approximated in these compounds because of lack of available field-effect transistors (FETs). Here we report the fabrication and room-temperature operation of FETs based on the hybrid perovskites. We obtained balanced electron and hole transport with mobilities of ∼1 cm2/Vs. We also found that the yield, as well as the operational and environmental stability of the fabricated transistors is limited.

Similar content being viewed by others

Inorganic perovskite materials have attracted significant research effort given their rich physical properties that includes high-temperature superconductivity, colossal magnetoresistance, ferroelectricity, diverse magnetic properties, etc.[1,2] Their structure has the general formula ABX3, where the cation B resides in the center of the corner sharing BX6 octahedra, the X anions occupy the corners; whereas cation A is surrounded by eight such octahedra (see, for example, SrTiO3, YMnO3, YVO3, and LaMnO3). The newest member of the perovskite family, namely the organic-inorganic perovskites, have recently emerged as an intriguing class of materials, which combine the low-cost processing and versatility characteristics to organic materials with the performance factors of inorganic compounds.[3,4] In particular, organo-lead halide perovskites (A+PbX3), where A+ is the organic cation and X denotes the halogen atom, have quickly become one of the hottest topics of research these days, in spite ofthe concerns related to the environmental hazard posed by the lead component. For example, the power conversion efficiency of hybrid perovskite photovoltaic (PV) solar cells has exceeded 19%,[5] and the light-emitting diodes (LEDs) based on these compounds rival the best on the market.[6] In addition, hybrid perovskite semiconductors exhibit wavelength-tunable photoluminescence (PL) emission,[7] laser action,[8] and charge carrier diffusion lengths of the order of hundreds of micrometers.[9] Surprisingly, these compounds also show interesting spin-related properties, including magneto-photocurrent, magneto-electroluminescence, and magneto-PL, in spite of their fast spin relaxation that is due to the strong spin–orbit coupling.[10,11] The hybrid perovskites based on methylammonium (where \({{\text{A}}^ + } = {\text{C}}{{\text{H}}_{\text{3}}}{\text{NH}}_3^ + \)) are most common, but other organic cations, such as ethylammonium \({\text{C}}{{\text{H}}_{\text{3}}}{\text{C}}{{\text{H}}_{\text{2}}}{\text{NH}}_3^ + \) or formamidinium \({\text{N}}{{\text{H}}_{\text{2}}}{\text{CH}} = {\text{NH}}_2^ + \) have also been explored.[12,13] It has been found that the anion (X = I, Br, Cl) impacts a variety of physical properties such as the crystal quality,[14] band-gap,[15] PV solar cell efficiency,[16] exciton-binding energy[17] and the amplified spontaneous emission wavelength.[8] Mixed halide perovskites such as CH3NH3PbI3−xClx, offer the possibility of fine tuning the physical properties that result from optimized film morphology,[18] and, in general exhibit higher conductivities and longer carrier diffusion lengths.[4]

The most exciting breakthroughs of hybrid halide perovskites are without a doubt in the area of PV technologies, where the new records in power conversion efficiencies have been reported at an unprecedented pace; in few years from the first report, the efficiency has improved by more than five times.[5,19–21] Necessary prerequisites for a material that forms an efficient solar cell are strong optical absorption and efficient charge carrier transport. Whereas the absorption spectrum has been routinely measured directly by the standard optical spectroscopy,[3,9,22] the charge transport properties were indirectly approximated from space charge-limited current,[9] Hall effect[7] and transient THz spectroscopy measurements.[23] These measurements have indicated the existence of an ambipolar, relatively high-mobility charge transport in the halide perovskites. This observation was further supported by the high-power conversion efficiencies measured in solar cell configurations where the hole-transporting layer is absent,[24] as well as by theoretical predictions.[7] Success in the fabrication of hybrid halide perovskite field-effect transistors (HHP-FETs) would unambiguously clarify the nature of charge transport in this class of materials, and promote the development of complementary optoelectronic applications, provided that the device performance is sufficiently high. In spite of several attempts on electrostatic gating of hybrid perovskite FETs, success has been rather limited.[25–27] In this paper, we report on the fabrication and room-temperature operation of FETs based on the halide hybrid perovskites. We obtained balanced electron and hole transport, in agreement with the high efficiency of PV cells based on these compounds, having mobilities of ~1cm2/Vs. We also found that the device fabrication yield, as well as the operational and environmental stability of the fabricated transistors is limited at the present time.

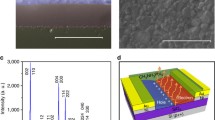

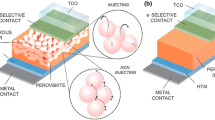

The crystal structure of the hybrid lead halide perovskites is shown in Fig. 1(a). The lead (yellow spheres) and halide (I/Cl, magenta spheres) occupy the sites at the centers and corners of the octahedron, respectively, whereas the organic cation sits in the interstices. Bottom-contact, top-gated FETs were fabricated on Au-patterned source and drain electrodes that were placed on an insulating substrate [see Fig. 1(b)]. The contacts were defined by photolithography and deposited using e-beam evaporation and lift-off. The substrates were cleaned in hot acetone and hot isopropyl alcohol, followed by UV–ozone and deionized water rinse. Prior to the deposition of the hybrid perovskite semiconductor layer, the electrodes were treated with 2,3,5,6-tetrafluoro-4-(trifluoromethyl)benzenethiol (TTFB, Sigma Aldrich) self-assembled monolayer (SAM) by immersing the substrate in a 50 mM solution in Ethanol (Sigma Aldrich) for 30 min, followed by ultrasonication in ethanol for 2 min. Subsequently, the perovskite layer was deposited from a precursor solution obtained by mixing of 0.8 g of CH3NH3I (Dyenamo) with 0.23 g of PbI2 and 0.42 g of PbCl2 (Sigma Aldrich) in 2.5 mL N,N-dimethylformamide solvent. The obtained solution was allowed to stir overnight on the hotplate at 70 °C in a nitrogen-filled glovebox (H2O, O2 < 1 ppm). Once cooled to room temperature, the bright yellow solution was spun coated on the pre-fabricated transistor substrates at 2000 RPM, a process that took place in the same glove-box. Subsequently, the films were annealed at 90 °C for 15 min, followed by a second annealing step at 105 °C for 120 min; this resulted in a change in color to a dark brown, indicating the formation of the CH3NH3PbI3−xClx perovskite layer. This was also confirmed by the UV-vis absorption and PL emission spectrum from the films [see Fig. 2(a)], which are in agreement with those previously measured on such films.[20,22] The perovskite film shows a broad absorption spectrum down to the near-infrared range, whereas its PL band that peaks at ~770 nm reveals an optical gap of ~1.6 eV. The absorption tail at energy below the optical gap is probably due to optical transitions into band tail states (i.e., Urbach edge) caused by traps and defects in the film, of which densities increase in thin perovskite films due to excess grain boundaries.[28] The x-ray diffraction (XRD) pattern [Fig. 2(b)] shows mainly the [110] and [220] diffraction lines, which originate from the preferential orientation of perovskite crystal domains, in agreement with high-quality solution-processed or co-evaporated films described in the literature.[29]

(a) The crystal structure of CH3NH3PbI3−xClx hybrid halide perovskite. The lead (yellow spheres) and halide (I/Cl, magenta spheres) sit at the centers and corners of the octahedron, respectively, and the organic cation sits in the interstices. (b) Schematic structure of the FETs based on hybrid halide semiconductor layer, having Au source and drain contacts, Cytop dielectric and Al gate electrode.

For the gate dielectric, a fluoropolymer—Cytop (Asahi Glass) layer was deposited from an un-diluted solution by spin coating in a nitrogen glove-box. The samples were subsequently annealed at 50 °C overnight in a vacuum oven to ensure crosslinking of the dielectric layer. Finally, Al top-gate electrode was deposited by thermal evaporation through a shadow mask [see Fig. 1(b) for the final device structure]. The samples were exposed to air between the different steps of the device processing.

Figure 3 shows current-voltage (I–V) characteristics for a FET device having channel length, L = 30 µm and channel width, W = 1000 µm. All measurements were performed in air, using an Agilent 4155C semiconductor parameter analyzer (with a voltage step of 0.2 V and using short integration time to minimize the bias stress effects). In Fig. 3(a), we plot the I–V characteristics measured at source-drain voltage, VDS = −30 V, where p-type transport is detected. The relativey noisy nature of the curves most probably originates from the fact that the measurement was fast, to prevent device degradation because of bias stress. A hole mobility, µh = 1. 3 cm2/Vs was calculated from the square-root dependence of the drain current ID versus the applied source-gate voltage, VGS (blue curve) using Eq. (1) below, where Ci is the dielectric capacitance per unit area (Ci = 1.3 nF/cm2, estimated based on the 1.4 µm dielectric thickness, and using a dielectric constant value of εr = 2.05, as quoted by Asahi Glass Co.):

As this curve shows deviations from a straight line, in Figs. 3(a) and 3(b) we marked in red the voltage range used in mobility estimation. The on/off ratio and the subthreshold slope, S, extracted from this I–V dependence were measured to be: on/off = 102 and S = 2.1 V/dec, respectively. The same device also showed electron transport [Fig. 3(b)] with an extracted mobility µe= 1.0 cm2/Vs, on/off ratio of 102 and S =1.5 V/dec. While the mobility and subthreshold slopes of our HHP-FET devices are on par with those of the best-reported organic FETs, the on/off ratio is significantly lower, most probably because of the relatively large off-current in the device due to the fact that the perovskite layer was not patterned.

FET devices with higher mobilities were also obtained; however, these values resulted from non-ideal transfer characteristics. Forthis reason we limit ourdiscussion to a conservative estimation of the charge carrier mobility. We also notice that the FET device yield is low so far, mostly because of the challenges in controlling the film wetting on the very hydrophobic surface created bythe TTFB treatment (with water contact angle of 107°). Work is in progress to understand this phenomenon, and improve the FET yield. Another possible reason for the low device yield is the partial degradation of the hybrid perovskite films prior to Cytop deposition. The modest robustness of the hybrid perovskite layer to environmental exposure is a well-known issue.[5] Cytop dielectric should also serve as an encapsulation layer; however, we noted that the devices degrade during several hours regardless of the storing conditions (vacuum, glove-box, and ambient air were tested). On the bright side, we found that some FET devices maintained good performance for several days; we are currently designing systematic experiments to understand this behavior. FETs on bottom SiO2 gate dielectric were also fabricated, but unfortunately no transistor behavior has been observed from such devices. For comparison, we also fabricated devices with Cytop dielectric, but without the TTFB contact treatment. We found that the yield in these devices is even lower, and the obtained transistor characteristics are not ideal, showing a sharp turn-on, followed by a lower slope, which is typically attributed to contact resistance. The maximum charge carrier mobility extracted from such devices was of the order of 0.1 cm2/Vs; however, because of the nature of the non-ideal I–V curves, we believe that this is an overestimation.

To understand the impact of the electrode surface chemical modification on the charge injection and transport, we estimated the shift in the work-function using Kelvin probe technique. A detailed description of this technique can be found in Ref. 30. We found that an increase of 0.41 ±0.02 eV was introduced upon SAM treatment, establishing an electrode work-function of 5.32 ± 0.02 eV. This value explains the successful hole-transport in the transistor channels; however, it cannot explain the electron injection due to the large Schottky barrier that forms here. We note that the conduction band minimum in the hybrid perovskites lies at −3.75 eV, and the valence band maximum is at −5.3 eV.[31] This observation demonstrates that when dealing with charge transport in HHP-FETs the energy band diagram picture does not always guarantee controlled charge injection. Here, charge injection and collection are probably dominated by the hybrid perovskite film morphology at the interface with the electrodes, and the resulting contact resistance.

The FET mobility values extracted from the obtained I–V measurements are lower than those measured using other electrical methods. The reason for that is that the charge carrier transport in FET devices is not only related to the quality of the perovskite layer, but also to the processes that occur at the semiconductor/dielectric interface, where interface states and low coordination bonds or dangling bonds may also impact conductivity. Excess roughness at this interface can also increase charge carrier scattering, which results in lower mobility. In addition, charge trapping at the grain-boundaries is known to inhibit charge transport. The perovskite films in our studies show typical roughness of 70 ± 10 nm, determined from atomic force microscopy (AFM) measurements [see Fig. 4(a)]; and grain sizes of the order of hundreds nm [see the scanning electron microscopy (SEM) image shown in Fig. 4(b)]. We therefore anticipate a substantial increase in mobility when increasing the grain size or working with perovskite single crystals, which may provide with the ultimate degree of order in these systems. We note that post-fabrication treatment using solvent annealing was already shown to increase grain size and enhance carrier diffusion lengths in the hybrid halide perovskites.[32]

In summary, we fabricated the first successful halide organic-inorganic hybrid perovskite FETs and measured their electrical characteristics at room temperature. We obtained balanced electron and hole-transport with mobilities of ~1 cm2/Vs. The processing temperature has not exceeded 105 °C, which ensures the compatibility with flexible plastic substrates where these devices can be manufactured using fast, large-area deposition methods such as inkjet printing, spray deposition, etc. This first generation devices, however suffer from short lifetimes and performance degradation during operation and/or storage, which may be improved at later time.

References

J.B. Goodenough: Metallic oxides. Progr. Solid State Chem. 5, 145 (1971).

B.B. Van Aken, T.T.M. Palstra, A. Filippetti, and N.A. Spaldin: The origin of ferroelectricity in magnetoelectric YMnO3. Nat. Mater. 3, 164 (2004).

M.A. Green, A. Ho-Baillie, and H.J. Snaith: The emergence of perovskite solar cells. Nat. Photonics 8, 506 (2014).

S.A. Bretschneider, J. Weickert, J.A. Dorman, and L. Schmidt-Mende: Research update: physical and electrical characteristics of lead halide perovskites for solar cell applications. APL Mater. 2, 040701 (2014).

H. Zhou, Q. Chen, G. Li, S. Luo, T.-B. Song, H.-S. Duan, Z. Hong, J. You, Y. Liu, and Y. Yang: Interface engineering of highly efficient perovskite solar cells. Science 345, 542 (2014).

Z.-K. Tan, R.S. Moghaddam, M.L. Lai, P. Docampo, R. Higler, F. Deschler, M. Price, A. Sadhanala, L.M. Pazos, D. Credgington, F. Hanusch, T. Bein, H.J. Snaith, and R.H. Friend: Bright light-emitting diodes based on organometal halide perovskite. Nat. Nano 9, 687 (2014).

C.C. Stoumpos, C.D. Malliakas, and M.G. Kanatzidis: Semiconducting tin and lead iodide perovskites with organic cations: phase transitions, high mobilities, and near-infrared photoluminescent properties. Inorg. Chem. 52, 9019 (2013).

G. Xing, N. Mathews, S.S. Lim, N. Yantara, X. Liu, D. Sabba, M. Grätzel, S. Mhaisalkar, and T.C. Sum: Low-temperature solution-processed wavelength-tunable perovskites for lasing. Nat. Mater. 13, 476 (2014).

Q. Dong, Y. Fang, Y. Shao, P. Mulligan, J. Qiu, L. Cao, and J. Huang: Electron–hole diffusion lengths >175 μm in solution-grown CH3NH3PbI3 single crystals. Science 347, 967 (2015).

C. Zhang, D. Sun, C.X. Sheng, Y.X. Zhai, K. Mielczarek, A. Zakhidov, and Z.V. Vardeny: Magnetic field effects in hybrid perovskite devices. Nat. Phys., doi:10.1038/nphys3277, Published online 16 March 2015.

D. Giovanni, H. Ma, J. Chua, M. Grätzel, R. Ramesh, S. Mhaisalkar, N. Mathews, and T.C. Sum: Highly spin-polarized carrier dynamics and ultralarge photoinduced magnetization in CH3NH3PbI3 perovskite thin films. Nano Lett. 15, 1553 (2015).

J.-H. Im, J. Chung, S.-J. Kim, and N.-G. Park: Synthesis, structure, and photovoltaic property of a nanocrystalline 2H perovskite-type novel sensitizer (CH3CH2NH3)PbI3. Nanoscale Res. Lett. 7, 353 (2012).

S. Pang, H. Hu, J. Zhang, S. Lv, Y. Yu, F. Wei, T. Qin, H. Xu, Z. Liu, and G. Cui: NH2CHvNH2PbI3: an alternative organolead iodide perovskite sensitizer for mesoscopic solar cells. Chem. Mater. 26, 1485 (2014).

Y. Tidhar, E. Edri, H. Weissman, D. Zohar, G. Hodes, D. Cahen, B. Rybtchinski, and S. Kirmayer: Crystallization of methyl ammonium lead halide perovskites: implications for photovoltaic applications. J. Am. Chem. Soc. 136, 13249 (2014).

J.H. Noh, S.H. Im, J.H. Heo, T.N. Mandal, and S.I. Seok: Chemical management for colorful, efficient, and stable inorganic–organic hybrid nanostructured solar cells. Nano Lett. 13, 1764 (2013).

B. Cai, Y. Xing, Z. Yang, W.-H. Zhang, and J. Qiu: High performance hybrid solar cells sensitized by organolead halide perovskites. Energy Environ. Sci. 6, 1480 (2013).

C.X. Sheng, C. Zhang, Y. Zhai, K. Mielczarek, W. Wang, W. Ma, A. Zakhidov, and Z.V. Vardeny: Exciton versus free carrier photogeneration in organometal trihalide perovskites probed by broadband ultrafast polarization memory dynamics. Phys. Rev. Lett. 114, 116601 (2015).

B.-W. Park, B. Philippe, T. Gustafsson, K. Sveinbjörnsson, A. Hagfeldt, E.M.J. Johansson, and G. Boschloo: Enhanced crystallinity in organic–inorganic lead halide perovskites on mesoporous TiO2 via disorder–order phase transition. Chem. Mater. 26, 4466 (2014).

A. Kojima, K. Teshima, Y. Shirai, and T. Miyasaka: Organometal halide perovskites as visible-light sensitizers for photovoltaic cells. J. Am. Chem. Soc. 131, 6050 (2009).

M.M. Lee, J. Teuscher, T. Miyasaka, T.N. Murakami, and H.J. Snaith: Efficient hybrid solar cells based on meso-superstructured organometal halide perovskites. Science 338, 643 (2012).

A. Mei, X. Li, L. Liu, Z. Ku, T. Liu, Y. Rong, M. Xu, M. Hu, J. Chen, Y. Yang, M. Grätzel, and H. Han: A hole-conductor-free, fully printable mesoscopic perovskite solar cell with high stability. Science 345, 295 (2014).

S.D. Stranks, G.E. Eperon, G. Grancini, C. Menelaou, M.J.P. Alcocer, T. Leijtens, L.M. Herz, A. Petrozza, and H.J. Snaith: Electron-hole diffusion lengths exceeding 1 micrometer in an organometal trihalide perovskite absorber. Science 342, 341 (2013).

C. Wehrenfennig, G.E. Eperon, M.B. Johnston, H.J. Snaith, and L.M. Herz: High charge carrier mobilities and lifetimes in organolead trihalide perovskites. Adv. Mater. 26, 1584 (2014).

L. Etgar, P. Gao, Z. Xue, Q. Peng, A.K. Chandiran, B. Liu, M.K. Nazeeruddin, and M. Grätzel: Mesoscopic CH3NH3PbI3/TiO2 heterojunction solar cells. J. Am. Chem. Soc. 134, 17396 (2012).

C.R. Kagan, D.B. Mitzi, and C.D. Dimitrakopoulos: Organic–inorganic hybrid materials as semiconducting channels in thin-film field-effect transistors. Science 286, 945 (1999).

D.B. Mitzi, C.D. Dimitrakopoulos, and L.L. Kosbar: Structurally tailored organic–inorganic perovskites: optical properties and solution-processed channel materials for thin-film transistors. Chem. Mater. 13, 3728 (2001).

X.Y. Chin, D. Cortecchia, J. Yin, A. Bruno, and C. Soci: Lead Iodide Perovskite Light-Emitting Field-Effect Transistor, arXiv:1501.04407, 2015.

S. De Wolf, J. Holovsky, S.-J. Moon, P. Löper, B. Niesen, M. Ledinsky, F.-J. Haug, J.-H. Yum, and C. Ballif: Organometallic halide perovskites: sharp optical absorption edge and its relation to photovoltaic performance. J. Phys. Chem. Lett. 5, 1035 (2014).

M. Liu, M.B. Johnston, and H.J. Snaith: Efficient planar heterojunction perovskite solar cells by vapour deposition. Nature 501, 395 (2013).

J.W. Ward, M.A. Loth, R.J. Kline, M. Coll, C. Ocal, J.E. Anthony, and O.D. Jurchescu: Tailored interfaces for self-patterning organic thin-film transistors. J. Mater. Chem. 22, 19047 (2012).

A. Abrusci, S.D. Stranks, P. Docampo, H.-L. Yip, A. K.Y. Jen, and H.J. Snaith: High-performance perovskite-polymer hybrid solar cells via electronic coupling with fullerene monolayers. Nano Lett. 13, 3124 (2013).

Z. Xiao, Q. Dong, C. Bi, Y. Shao, Y. Yuan, and J. Huang: Solvent annealing of perovskite-induced crystal growth for photovoltaic-device efficiency enhancement. Adv. Mater. 26, 6503 (2014).

Acknowledgments

We acknowledge the Office of Naval research for support. We also acknowledge the Utah NSF-MRSEC for supporting the acquisition and development of the glove-box/metal evaporation facility in the department of P&A at the University of Utah.

Author information

Authors and Affiliations

Corresponding authors

Additional information

† Authors contributed equally to the work.

An earlier version of this article published with authors listed in the incorrect order. For more information see doi: 10.1557/mrc.2015.33.

Rights and permissions

This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Mei, Y., Zhang, C., Vardeny, Z.V. et al. Electrostatic gating of hybrid halide perovskite field-effect transistors: balanced ambipolar transport at room-temperature. MRS Communications 5, 297–301 (2015). https://doi.org/10.1557/mrc.2015.21

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1557/mrc.2015.21