Abstract

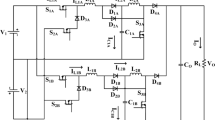

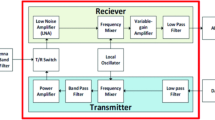

In view of changing the type of energy conversion in CMOS circuits, this paper investigates low power CMOS circuit design, which adopts a gradually changing power clock. First, we discuss the algebraic expressions and the corresponding properties of clocked power signals. Then the design procedure is summed up for converting complementary CMOS logic gates employing DC power to the power-clocked CMOS gates employing AC power. On this basis, the design of differential cascode voltage switch logic (DCVSL) circuits employing AC power clocks is proposed. The PSPICE simulations using a sinusoidal power-clock demonstrate that the designed power-clocked DCVSL circuit has a correct logic function and low power characteristics. Finally, an interface circuit to convert clocked signals into the standard logic levels of a CMOS circuit is proposed, and its validity is verified by computer simulations.

Similar content being viewed by others

References

Weste, N., Eshraghian, K., Principles of CMOS VLSI Design: A Systems Perspective, 2nd ed., New York: Addison-Wesley, 1993.

Pedram, M., Power minimization in IC design: principles and applications, ACM Transactions on Design Automaton of Electronic Systems, 1996, 1(1): 3–56.

Athas, W. C., Svensson, L. J., Koller, J. G. et al., Low-power digital systems based on adiabatic-switching principles, IEEE Trans. on VLSI Systems, 1994, 2(4): 398–407.

Denker, J. S., A review of adiabatic computing, in Proc. of the Symposium on Low Power Electronics, San Diego: IEEE, 1994, 94–97.

Denker, J. S., Avery, S. C., Dickinson, A. G. et al., Adiabatic computing with the 2N-2N2D logic family, in Proc. of the International Workshop on Low Power Design, Napa Valley, 1994, 183–187.

Dickinson, A. G., Denker, J. S. Adiabatic dynamic logic, IEEE J. of Solid-State Circuits, 1995, 30(3): 311–315.

Kamer, A., Denker, J. S., Flower, B. et al., 2ND order adiabatic computation with 2N-2P and 2N-2N2P logic circuits, in Proc. of the International Symposium on Low Power Design, Monterey, New York: IEEE, 1995, 191–196.

Maksimovic, D., Oklobdzija, V. C., Nikolic, B. et al., Clocked CMOS adiabatic logic with integrated single-phase power-clock supply: experimental results, in Proc. of the International Symposium on Low-Power Electronics and Design, Monterey, New York: IEEE, 1997, 323–327.

Oklobdzija, V. C., Maksimovic, D., Lin, F., Pass-transistor adiabatic logic using single-clock supply, IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing, 1997, 44(10): 842–846.

Moon, Y., Jeong, D. K., An efficient charge recovery logic circuit, IEEE J. of Solid-State Circuits, 1996, SC-31(4): 514–522.

Kim, S., Papaefthymiou, M. C., True single-phase-recovering logic for low-power, high-speed VLSI, in Proc. of the International Symposium on Low-Power Electronics and Design, Monterey, New York: IEEE, 1998, 167–172.

Wu, X., Pedram, M., Low power CMOS circuits with alternative power supply, in Proc. China Eleventh Conference on Integrated Circuits and Silicon Materials (in Chinese), 1999, 688–691.

Pedram, M., Wu, X., Analysis of power-clocked CMOS with application to the design of energy-recovery circuits, in Proc. of ASP-DAC, Pacifico Yokohama, 2000, 339–344.

Wu, X., Theory of transmission switches and its application to design of CMOS digital circuits, Int. J. of Circuit Theory and Application, 1992, 20(4): 349–356.

Heller, L. G., Griffin, W. R., Davis, J. W. et al., Cascode voltage switch logic: a differential CMOS logic family, in Proc. Int. Conf. on Solid-State Circuits, San Francisco, 1984, 16–17.

Chu, K. M., Pulfrey, D. L., A comparison of CMOS circuit technique: differential cascode voltage switch logic versus conventional logic, IEEE J. of Solid-State Circuits, 1987, SC-24: 779–786.

Wu, X., Hang, G., Principle of adiabatic computing and CMOS circuits with energy recovery, Chinese J. Computers (in Chinese), 2000, 23(7): 779–785.

Wu, X., Hang, G., Energy recovery circuits with cross-coupled structure, J. of Circuits and Systems (in Chinese), 2000, 5(2), 1–8.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wu, X., Hang, G. & Massoud, P. Low power DCVSL circuits employing AC power supply. Sci China Ser F 45, 232–240 (2002). https://doi.org/10.1360/02yf9021

Received:

Issue Date:

DOI: https://doi.org/10.1360/02yf9021