Abstract

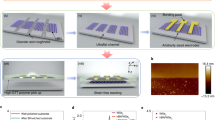

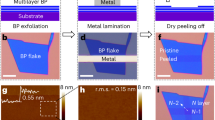

Two-dimensional semiconductors such as layered transition metal dichalcogenides can offer superior immunity to short-channel effects compared with bulk semiconductors such as silicon. As a result, these materials can be used to create highly scaled transistors. However, on-state current densities of two-dimensional semiconductor transistors are still below those of silicon transistors. Here we show that bilayer tungsten diselenide transistors that have channel lengths of less than 100 nm can exhibit on-state current densities above 1.0 mA μm−1 and on-state resistances below 1.0 kΩ μm at room temperature. The devices have atomically clean van der Waals vanadium diselenide contacts and are created using van der Waals epitaxy and controlled crack formation processes. With a 20-nm-long and 1.3-nm-thick transistor, an on-state current density of 1.72 mA μm−1 and on-state resistance of 0.50 kΩ μm are achieved, showing comparable performance to silicon transistors with similar channel lengths and driving voltages.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

Change history

14 November 2022

A Correction to this paper has been published: https://doi.org/10.1038/s41928-022-00891-y

References

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

Huang, J. K. et al. Large-area synthesis of highly crystalline WSe2 monolayers and device applications. ACS Nano 8, 923–930 (2014).

Cheng, R. et al. Few-layer molybdenum disulfide transistors and circuits for high-speed flexible electronics. Nat. Commun. 5, 5143 (2014).

Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Liu, Y. et al. Two-dimensional transistors beyond graphene and TMDCs. Chem. Soc. Rev. 47, 6388–6409 (2018).

Vu, Q. A. et al. Near-zero hysteresis and near-ideal subthreshold swing in h-BN encapsulated single-layer MoS2 field-effect transistors. 2D Mater. 5, 0310013 (2018).

Lee, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Li, M.-Y., Su, S.-K., Wong, H.-S. P. & Li, L.-J. How 2D semiconductors could extend Moore’s law. Nature 567, 169–170 (2019).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Liu, C. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).

Sakaki, H. et al. Interface roughness scattering in GaAs/AlAs quantum wells. Appl. Phy. Lett. 51, 1934–1936 (1987).

Poljak, M. et al. Assessment of electron mobility in ultrathin-body InGaAs-on-insulator MOSFETs using physics-based modeling. IEEE Trans. Electron Devices 59, 1636–1643 (2012).

Jena, D. Tunneling transistors based on graphene and 2D crystals. Proc. IEEE 101, 1585–1602 (2013).

Liu, H., Neal, A. T. & Ye, P. D. D. Channel length scaling of MoS2 MOSFETs. ACS Nano 6, 8563–8569 (2012).

Kappera, R. et al. Phase-engineered low-resistance contacts for ultrathin MoS2 transistors. Nat. Mater. 13, 1128–1134 (2014).

Cho, S. et al. Phase patterning for ohmic homojunction contact in MoTe2. Science 349, 625–628 (2015).

Cui, X. et al. Multi-terminal transport measurements of MoS2 using a van der Waals heterostructure device platform. Nat. Nanotechnol. 10, 534–540 (2015).

Bandurin, D. A. et al. High electron mobility, quantum Hall effect and anomalous optical response in atomically thin InSe. Nat. Nanotechnol. 12, 223–227 (2017).

Zhang, X. et al. Low contact barrier in 2H/1T′ MoTe2 in-plane heterostructure synthesized by chemical vapor deposition. ACS Appl. Mater. Interfaces 11, 12777–12785 (2019).

Cao, W., Kang, J., Liu, W. & Banerjee, K. A compact current–voltage model for 2D semiconductor-based field-effect transistors considering interface traps, mobility degradation, and inefficient doping effect. IEEE Trans. Electron Devices 61, 4282–4290 (2014).

Collaert, N. Device architectures for the 5nm technology node and beyond. Semicon, Taiwan (2016). https://bjpcjp.github.io/pdfs/chips/SEMICON_Taiwan_2016_collaert.pdf

Huyghebaert, C. et al. 2D materials: roadmap to CMOS integration. In 2018 IEEE International Electron Devices Meeting (IEDM) 22.1.1−22.1.4 (IEEE, 2018).

Wang, X. et al. Van der Waals negative capacitance transistors. Nat. Commun. 10, 3037 (2019).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Liu, W. et al. Role of metal contacts in designing high-performance monolayer n-type WSe2 field effect transistors. Nano Lett. 13, 1983–1990 (2013).

Perera, M. M. et al. Improved carrier mobility in few-layer MoS2 field-effect transistors with ionic-liquid gating. ACS Nano 7, 4449–4458 (2013).

Chang, H. Y. et al. High-performance, highly bendable MoS2 transistors with high-k dielectrics for flexible low-power systems. ACS Nano 7, 5446–5452 (2013).

Yang, L. et al. Chloride molecular doping technique on 2D materials: WS2 and MoS2. Nano Lett. 14, 6275–6280 (2014).

Chuang, H. J. et al. Low-resistance 2D/2D ohmic contacts: a universal approach to high-performance WSe2, MoS2, and MoSe2 transistors. Nano Lett. 16, 1896–1902 (2016).

LaGasse, S. W. et al. Gate‐tunable graphene–WSe2 heterojunctions at the Schottky–Mott limit. Adv. Mater. 31, 190139224 (2019).

Smets, Q. et al. Ultra-scaled MOCVD MoS2 MOSFETs with 42nm contact pitch and 250µA/µm drain current. In 2019 IEEE International Electron Devices Meeting (IEDM) 23.2.1–23.2.4 (IEEE, 2019).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Radu, I. 2D materials in the logic roadmap: 5 good reasons and 3 major challenges. https://www.edn.com/2d-materials-in-the-logic-roadmap-5-good-reasons-and-3-major-challenges/ (2021).

Xia, J. L. et al. Effect of top dielectric medium on gate capacitance of graphene field effect transistors: implications in mobility measurements and sensor applications. Nano Lett. 10, 105060–105064 (2010).

Fuhrer, M. & Hone, J. Measurement of mobility in dual-gated MoS2 transistors. Nat. Nanotechnol. 8, 146–147 (2013).

Nasr, J. R. et al. Mobility deception in nanoscale transistors: an untold contact story. Adv. Mater. 31, 1806020 (2019).

Ueng, H. J., Janes, D. B. & Webb, K. J. Error analysis leading to design criteria for transmission line model characterization of ohmic contacts. IEEE Trans. Electron Devices 48, 758–766 (2001).

Qiu, C. et al. Scaling carbon nanotube complementary transistors to 5-nm gate lengths. Science 355, 271–276 (2017).

Smithe, K. et al. Low variability in synthetic monolayer MoS2 devices. ACS Nano 11, 8456–8463 (2017).

Mookerjea, S. et al. Effective capacitance and drive current for tunnel FET (TFET) CV/I estimation. IEEE Trans. Electron Devices 56, 2092–2098 (2009).

Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. Intrinsic electrical transport and performance projections of synthetic monolayer MoS2 devices. 2D Mater. 4, 011009 (2017).

Rhodes, D., Chae, S. H., Ribeiro-Palau, R. & Hone, J. Disorder in van der Waals heterostructures of 2D materials. Nat. Mater. 18, 541–549 (2019).

Mack, C. A. Field Guide to Optical Lithography Vol. 6 (SPIE Press, 2006).

Zan, R. et al. Control of radiation damage in MoS2 by graphene encapsulation. ACS Nano 7, 10167–10174 (2013).

Yang, Y., Gu, C. & Li, J. Sub‐5 nm metal nanogaps: physical properties, fabrication methods, and device applications. Small 15, 1804177 (2019).

McClellan, C. J., Yalon, E., Smithe, K. K. H., Suryavanshi, S. V. & Pop, E. High current density in monolayer MoS2 doped by AlOx. ACS Nano 15, 1587–1596 (2021).

Li, J. et al. General synthesis of two-dimensional van der Waals heterostructure arrays. Nature 579, 368–374 (2020).

Shen, P. C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Zhang, Z. et al. Ultrafast growth of large single crystals of monolayer WS2 and WSe2. Natl Sci. Rev. 7, 737–744 (2020).

Wiegers, G. A. The characterization of VSe2: a study of the thermal expansion. J. Phys. C: Solid State Phys. 14, 4225 (1981).

Ahn, G. H. et al. Strain-engineered growth of two-dimensional materials. Nat. Commun. 8, 608 (2017).

Tada, H. et al. Thermal expansion coefficient of polycrystalline silicon and silicon dioxide thin films at high temperatures. J. Appl. Phys. 87, 4189–4193 (2000).

Zhou, H. et al. Large area growth and electrical properties of p-type WSe2 atomic layers. Nano Lett. 15, 709–713 (2015).

Zhang, Z. et al. Van der Waals epitaxial growth of 2D metallic vanadium diselenide single crystals and their extra‐high electrical conductivity. Adv. Mater. 29, 17023592017 (2017).

Frank, D. J. et al. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 89, 259–288 (2001).

Kumar, A. & Ahluwalia, P. K. Tunable dielectric response of transition metals dichalcogenides MX2 (M = Mo, W; X = S, Se, Te): effect of quantum confinement. Phys. B 407, 4627–4634 (2012).

Semiconductor, V. The general properties of Si, Ge, SiGe, SiO2 and Si3N4. (2002). https://www.virginiasemi.com

Sun, X. et al. Performance limit of monolayer WSe2 transistors; significantly outperform their MoS2 counterpart. ACS Appl. Mater. Interfaces 12, 20633–20644 (2020).

Li, X. et al. High-speed black phosphorus field-effect transistors approaching ballistic limit. Sci. Adv. 5, eaau3194 (2019).

Zhong, M. et al. Thickness-dependent carrier transport characteristics of a new 2D elemental semiconductor: black arsenic. Adv. Funct. Mater. 28, 1802581 (2018).

Yuan, S. et al. Air-stable room-temperature mid-infrared photodetectors based on hBN/black arsenic phosphorus/hBN heterostructures. Nano Lett. 18, 3172–3179 (2018).

Liu, Y. et al. Pushing the performance limit of sub-100 nm molybdenum disulfide transistors. Nano Lett. 16, 6337–6342 (2016).

Chou, A. et al. High on-current 2D nFET of 390 µA/µm at VDS = 1V using monolayer CVD MoS2 without intentional doping. In 2020 IEEE Symposium on VLSI Technology 1–2 (IEEE, 2020).

Pang, C.-S., Wu, P., Appenzeller, J. & Chen, Z. Sub-1nm EOT WS2-FET with IDS > 600μA/μm at VDS=1V and SS < 70mV/dec at LG=40nm. In 2020 IEEE International Electron Devices Meeting (IEDM) 3.4.1−3.4.4 (IEEE, 2020).

Iqbal, M. W. et al. High-mobility and air-stable single-layer WS2 field-effect transistors sandwiched between chemical vapor deposition-grown hexagonal BN films. Sci. Rep. 5, 10699 (2015).

He, Q. et al. Molecular beam epitaxy scalable growth of wafer‐scale continuous semiconducting monolayer MoTe2 on inert amorphous dielectrics. Adv. Mater. 31, 1901578 (2019).

Guo, J. et al. Few-layer GeAs field-effect transistors and infrared photodetectors. Adv. Mater. 30, 1705934 (2018).

Huang, Y.-T. et al. High-performance InSe transistors with ohmic contact enabled by nonrectifying barrier-type indium electrodes. ACS Appl. Mater. Interfaces 10, 33450–33456 (2018).

Yang, S. et al. Highly-anisotropic optical and electrical properties in layered SnSe. Nano Res. 11, 554–564 (2018).

Shim, J. et al. High-performance 2D rhenium disulfide (ReS2) transistors and photodetectors by oxygen plasma treatment. Adv. Mater. 28, 6985–6992 (2016).

Yang, S. et al. Layer-dependent electrical and optoelectronic responses of ReSe2 nanosheet transistors. Nanoscale 6, 7226–7231 (2014).

Mleczko, M. J. et al. HfSe2 and ZrSe2: two-dimensional semiconductors with native high-κ oxides. Sci. Adv. 3, e1700481 (2017).

Zhao, Y. et al. High-electron-mobility and air-stable 2D layered PtSe2 FETs. Adv. Mater. 29, 1604230 (2017).

The International Technology Roadmap for Semiconductors. http://www.itrs2.net/itrs-reports.html

Sebastian, A. et al. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 12, 693 (2021).

Baliga, J. in Modern Power Devices 148–149 (Wiley, 1987).

Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 557, 696–700 (2018).

Liu, Y., Huang, Y. & Duan, X. Van der Waals integration before and beyond two-dimensional materials. Nature 567, 323–333 (2019).

Acknowledgements

The authors at Hunan University acknowledge support from the National Key Research and Development Program of China (grant no. 2018YFE0202700), National Natural Science Foundation of China (nos. 51802090, 51872086, 51991343, 51991341, 51991340 and 61874041), the Hunan Key Laboratory of Two-Dimensional Materials (grant no. 2018TP1010) and the Innovative Research Groups of Hunan Province (grant no. 2020JJ1001).

Author information

Authors and Affiliations

Contributions

Xidong Duan conceived the research. R.W. developed a lithography-free approach to sub-100-nm channel lengths and measured all the devices. Q.T., W.L., Y.C., Z.S., H.D. and L.L. performed the device fabrication. J.L. participated in the investigation of the crack formation mechanism. J.L., H.M. and B.Z. participated in materials growth as well as TEM and HAADF-STEM characterizations. R.W., Q.T., Z.Z., X.Y., B.L. and Y.L. contributed to the discussions and data analysis. Xidong Duan supervised the research. R.W., Xidong Duan and Xiangfeng Duan co-wrote the manuscript with inputs from all the authors. All the authors discussed the results and commented on the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Jing Lu and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data

Extended Data Fig. 1 The Raman and PL spectrum of the VSe2/WSe2.

a, b Raman spectrum and PL spectrum obtained from the measurement area on both sides of the crack of VSe2/WSe2, respectively.

Extended Data Fig. 2 Electron microscopy characterizations of the sub-100 nm bilayer WSe2 transistors.

a, The SAED pattern of the bare WSe2. b, The SAED pattern collected from the overlapping VSe2/WSe2 region shows two sets of electron diffraction patterns, corresponding to WSe2 and VSe2, respectively. The insets in (a, b) show a magnified view of a selected area electron diffraction spot. The diffraction spots from the overlapping VSe2/WSe2 area shows two sets of identically orientated diffraction spots with the inner and outer set corresponding to the 1T-VSe2 and 2H-WSe2. (c) HAADF-STEM image taken on the bare WSe2 region with a lattice constant of 3.29 Å for of WSe2. (d) HAADF-STEM image taken on the VSe2 region show a lattice constant of 3.36 Å for VSe2. Scale bars: a, b 2 nm−1; c, d 2 nm.

Extended Data Fig. 3 Energy dispersive spectroscopy (EDS) elemental mapping image.

The distribution of the entire element mapping image of the cross-sectional image of (VSe2/WSe2)–WSe2–(VSe2/WSe2) device supported on the 70 nm SiNx substrate. Scale bar: 20 nm.

Extended Data Fig. 4 Electrical characterizations of 10 sub-100 nm WSe2 devices.

a1 - j2, The output and transfer curves of 10 sub-100 nm WSe2 devices at room temperature. The Vgs varies with a 5 V step in the output curves.

Extended Data Fig. 5 Electrical characteristics of the sub-100 nm monolayer WSe2 transistors.

a, Output characteristics of the 72-nm-length monolayer WSe2 transistors at various back-gate voltages with a step of 5 V. The inset shows the SEM image of the monolayer WSe2 transistor with 72 nm channel length. Scale bars: 100 nm. b, Transfer curves of the 72-nm-length monolayer WSe2 transistor at various bias voltages.

Extended Data Fig. 6 Top-gated ultra-short channel bilayer WSe2 transistor.

a, SEM image of the top-gated bilayer WSe2 transistor with ~3 nm Al2O3/6 nm HfO2 as top-gate dielectrics. The length and width of the WSe2 transistor are 80 nm and 6.0 μm. The scale of inset is 5 μm. b, Transfer curves of the 80-nm-length transistor at various bias voltages when Vbg is fixed at −30 V. c, Output characteristics of the 80-nm-length WSe2 transistor at various top-gate voltages with a step of 1 V.

Extended Data Fig. 7 Ultrashort WSe2 channel array with VSe2 contacts generated by synthesis of WSe2/VSe2 vdW heterostructure array and following controlled crack formation process.

a, The OM images of 1 × 6 ultrashort channels of WSe2 array with VSe2 synthetic contacts. b-f, The corresponding SEM images of a. Scale bars: 1 μm.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Wu, R., Tao, Q., Li, J. et al. Bilayer tungsten diselenide transistors with on-state currents exceeding 1.5 milliamperes per micrometre. Nat Electron 5, 497–504 (2022). https://doi.org/10.1038/s41928-022-00800-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-022-00800-3

This article is cited by

-

Ultrashort vertical-channel MoS2 transistor using a self-aligned contact

Nature Communications (2024)

-

Two-dimensional perovskite oxide as a photoactive high-κ gate dielectric

Nature Electronics (2024)

-

Phase-engineered synthesis of atomically thin te single crystals with high on-state currents

Nature Communications (2024)

-

Van der Waals Heterostructure Engineering for Ultralow-Resistance Contact in 2D Semiconductor P-Type Transistors

Journal of Electronic Materials (2024)

-

The Roadmap of 2D Materials and Devices Toward Chips

Nano-Micro Letters (2024)