Abstract

Modern processors embed features such as pipelined execution units and cache memories that can not be directly controlled by programmers through the processor instruction set. As a result, software-based fault injection approaches are even less suitable for assessing the effects of SEUs in modern processors, since they are not able to evaluate the effects of SEUs affecting pipelines and caches. In this paper we report an analysis of a commercial processor core where the effects of SEUs located in the processor pipeline and cache memories are studied. The obtained results are compared with those software-based approaches provide, showing that software-based approaches may lead to significant errors during the error rate estimation. A major novelty of the paper is an extensive analysis of the effects of SEUs in the pipeline of a commercial processor core during the execution of several benchmark programs.

Similar content being viewed by others

References

P.L. Civera, L. Macchiarulo, M. Rebaudengo, M. Sonza Reorda, and M. Violante, “FPGA-Based Fault Injection for Microprocessor Systems,” in Proc. IEEE Asian Test Symposium, 2001, pp. 304-309.

E. Dupont, M. Nicolaidis, and P. Rohr, “Embedded Robustness IPs for Transient-Error-Free ICs,” IEEE Design and Test of Computers, vol. 19, no. 3, pp. 560-570, 2002.

J. Gracia, J.C. Baraza, D. Gil, and P.J. Gil, “A Study of the Experimental Validation of Fault-Tolerant Systems Using Different VHDL-Based Fault Injection Techniques,” in Proc. IEEE International On-Line Testing Workshop, 2000, pp. 73-79.

R.K. Iyer and D. Tang, “Experimental Analysis of Computer System Dependability,” Chapter 5 of Fault-Tolerant Computer System Design, D.K. Pradhan (Ed.), Prentice Hall, 1996.

M. Nicolaidis, “Time Redundancy Based Soft-Error Tolerance to Rescue Nanometer Technologies,” in Proc. IEEE 17th VLSI Test Symposium, April 1999, pp. 86-94.

B. Parrotta, M. Rebaudengo, M. Sonza Reorda, and M. Violante, “New Techniques for Accelerating Fault Injection in VHDL Descriptions,” in Proc. IEEE International On-Line Test Workshop, 2000, pp. 61-66.

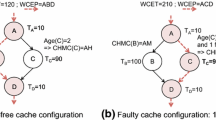

M. Rebaudengo, M. Sonza Reorda, and M. Violante, “An Accurate Analysis of the Effects of Soft Errors in the Instruction and Data Caches of a Pipelined Microprocessor,” in DATE2003: Design, Automation and Test in Europe, 2003, pp. 602-607.

R. Velazco, S. Rezgui, and R. Ecoffet, “Predicting Error Rate for Microprocessor-Based Digital Architectures Through C.E.U. (Code Emulating Upsets) Injection,” IEEE Transactions on Nuclear Science, vol. 47, no. 6, pp. 2405-2411, 2000.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Rebaudengo, M., Reorda, M.S. & Violante, M. Accurate Analysis of Single Event Upsets in a Pipelined Microprocessor. Journal of Electronic Testing 19, 577–584 (2003). https://doi.org/10.1023/A:1025130131636

Issue Date:

DOI: https://doi.org/10.1023/A:1025130131636