Abstract

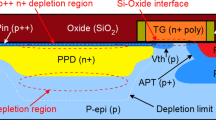

A double photodiode (PD) constructed by p+/N-well junction and N-well/p-sub junction was designed and fabricated in a UMC 0.18-μm CMOS process. Based on the device structure and mechanism of double PD, a novel small-signal equivalent circuit model considering the carrier transit effect and the parasitic RC time constant was presented. By this model with complete electronic components, the double PD can be incorporated in a commercial circuit simulator. The component values were extracted by fitting the measured S-parameters using simulated annealing algorithm, and a good agreement between the measurement and the simulation results was achieved.

Similar content being viewed by others

References

Zhou ZP, Tu ZJ, Li TT et al (2015) Silicon photonics for advanced optical interconnections. J Lightwave Technol 33:928–933

Jonathan KD, Andrew PK (2012) The evolution of silicon photonics as an enabling technology for optical interconnection. Laser Photonics Rev 6:504–525

Xie S, Tao XZ, Mao LH et al (2016) High-Gm differential regulated cascode transimpedance amplifier. Trans Tianjin Univ 22:345–351

Behrooz N, Sagar R, Mona MH (2012) High speed photodiodes in standard nanometer scale CMOS technology: a comparative study. Opt Express 20:11256–11270

Tang L, Latif S, Miller DAB (2009) Plasmonic device in silicon CMOS. Electron Lett 45:706–708

Huang SH, Chen WZ, Chang YW et al (2011) A 10-Gb/s OEIC with meshed spatially-modulated photo detector in 0.18-µm CMOS technology. IEEE J Solid-State Circuits 46:1158–1169

Pan Q, Hou ZX, Wang YP et al (2014) A 48-mW 18-Gb/s fully integrated CMOS optical receiver with photodetector and adaptive equalizer. IEEE symposium on VLSI circuits—digest of technical paper: 6858402

Chen WY, Liu SY (1996) PIN avalanche photodiodes model for circuit simulation. IEEE J Quantum Electron 32:2105–2111

Wu JY, Wang G (2010) A novel equivalent circuit model for separate absorption grading charge multiplication avalanche photodiode (APD)-based optical receiver. J Lightwave Technol 28:784–790

Lee MJ, Kang HS, Choi WY (2008) Equivalent circuit model for Si avalanche photodetectors fabricated in standard CMOS process. IEEE Electron Device Lett 29:1115–1117

Mao LH, Chen HD, Wu RH et al (2002) Simulation and design of a CMOS-process-compatible high-speed Si-photodetector. Chin J Semicond 23:193–197 (in Chinese)

Dai DX, Piels M, Bowers JE (2014) Monolithic germanium/silicon photodetectors with decoupled structures: resonant APDs and UTC photodiodes. IEEE J Sel Top Quantum Electron 20:3802214

Lu CN, Sou G, Devigny F et al (2001) Design and testing of a CMOS BDJ detector for integrated micro-analysis systems. Microelectron J 32:227–234

Paul DH, Dylan FW (2003) Calibrated measurement of optoelectronic frequency response. IEEE Trans Microwave Theory 51:1422–1429

Mohammad S, Ali J (2015) An evolutionary-based methodology for symbolic simplification of analog circuits using genetic algorithm and simulated annealing. Expert Syst Appl 42:1189–1201

Kazutoshi K, Susumu H, Kenji K et al (1993) Design of ultrawide-band, high-sensitivity p-i-n photodetectors. IEICE Trans Electron E76-C:214–221

Acknowledgements

This study was supported by the National Natural Science Foundation of China (No. 61474081) and Guangxi Key Laboratory of Precision Navigation Technology and Application, Guilin University of Electronic Technology (No. DH201513).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Xie, S., Luo, X., Mao, L. et al. Design, Fabrication, and Modeling of CMOS-Compatible Double Photodiode. Trans. Tianjin Univ. 23, 163–167 (2017). https://doi.org/10.1007/s12209-017-0038-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12209-017-0038-1