Abstract

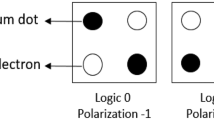

QCA is an emerging nanotechnology for the design of digital system circuits based on electron interactions. QCA is used to design nanoscale circuits. Multiplier algorithms play an important role in computer computing, and algorithms with better performance speeds are more considerable. Booth multiplication algorithm is one of the multiplication algorithms that increases the multiplication speed by decreasing the number of partial products and using a smaller adder. In this paper, the Booth multiplication algorithm is designed and implemented in QCA. It has been tried to contain minimum number of cells and the least complexity and energy dissipation in the proposed design.

Similar content being viewed by others

Explore related subjects

Discover the latest articles and news from researchers in related subjects, suggested using machine learning.References

Mano M (1993) Computer System Architecture, 3rd edn. Prentice-Hall International Editions Inc., Upper Saddle River

Rajadurai S, Alazab M, Kumar N, Gadekallu TR (2020) Latency evaluation of SDFGs on heterogeneous processors using timed automata. IEEE Access 8:140171–140180

Marco A, Shen W-Z (1984) The design of an LSI Booth multiplier: nMOS vs. CMOS technology

Kishore S, Kureshi D (2016) Hardware implementation of configurable booth multiplier on FPGA. Int J VLSI Des Commun 4(1):99–103

Lent C, Tougaw P (1997) A device architecture for computing with quantum dots. Proc IEEE 85(4):541–557

Yu W, Zhang B, Liu C, Zhao Y, Wu WR, Xue ZY, Chen M, Buca D, Hartmann J-M, Wang X, Zhao QT, Mantl S (2014) Impact of Si cap, strain and temperature on the hole mobility of (s)Si/sSiGe/(s)SOI quantum-well p-MOSFETs. Microelectr Eng 113:5–9. https://doi.org/10.1016/j.mee.2013.06.015

Bose R, Johnson HT (2004) Coulomb interaction energy in optical and quantum computing applications of self-assembled quantum dots. Microelectr Eng 75(1):43–53. https://doi.org/10.1016/j.mee.2003.11.008

Asfestani MN, Heikalabad SR (2017a) A unique structure for the multiplexer in quantum-dot cellular automata to create a revolution in design of nanostructures. Phys B Condens Matter 512:91–99

Chabi AM et al (2017) Towards ultra-efficient QCA reversible circuits. Microprocess Microsyst 49:127–138

Ahmad F et al (2016) Towards single layer quantum-dot cellular automata adders based on explicit interaction of cells. J Comput Sci 16:8–15

Roohi A, DeMara RF, Khoshavi N (2015a) Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron J 46(6):531–542

Walus K et al (2004) QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3(1):26–31

Heikalabad SR, Navin AH, Hosseinzadeh M (2015) Midpoint memory: a special memory structure for data-oriented models implementation. J Circ Syst Comput 24(5):1550063

Heikalabad SR, Navin AH, Hosseinzadeh M (2016) Content addressable memory cell in quantum-dot cellular automata. Microelectron Eng 163:140–150

Karkaj ET, Heikalabad SR (2017) Binary to gray and gray to binary converter in quantum-dot cellular automata. Opt Int J Light Electron Opt. https://doi.org/10.1016/j.ijleo.2016.11.087

Lent CS, Tougaw PD, Porod W (1993) Bistable saturation in coupled quantum dots for quantum cellular automata. Appl Phys Lett 62(7):714–716

Roohi A, DeMara RF, Khoshavi N (2015b) Design and evaluation of anultra-area-efficient fault-tolerant QCA full adder. Microelectron J 46(6):531–542

Ahmadpour S-S, Mosleh M, Heikalabad SR (2018) A revolution in nanostructure designs by proposing a novel QCA full-adder based on optimized 3-input XOR. Phys B: Condens Matter 550:383–392

Salimzadeh F, Heikalabad SR (2019) Design of a novel reversible structure for full adder/subtractor in quantum-dot cellular automata. Phys B: Condens Matter 556:163–169

Heikalabad SR, Kamrani H (2019) Design and implementation of circuit-switched network based on nanoscale quantum-dot cellular automata. Photon Netw Commun 38(3):356–377

Norouzi Ali, Heikalabad Saeed Rasouli (2019) Design of reversible parity generator and checker for the implementation of nano-communication systems in quantum-dot cellular automata. Photon Netw Commun 38(2):231–243

Milad B, Mahya S, Alireza A, Keivan N, Nader B (2016) A 3D universal structure based on molecular-QCA and CNT technologies. J Mol Struct 1119:86–95. https://doi.org/10.1016/j.molstruc.2016.04.025

Mohammad M, Majid M, Saeid G (2016) An efficient design of full adder in quantum-dot cellular automata (QCA) technology. Microelectr J 50:35–43. https://doi.org/10.1016/j.mejo.2016.02.004

Karkaj ET, Heikalabad SR (2016) A testable parity conservative gate in quantum-dot cellular automata. Superlattices Microstruct. https://doi.org/10.1016/j.spmi.2016.08.054

Asfestani MN, Heikalabad SR (2017b) A novel multiplexer-based structure for random access memory cell in quantum-dot cellular automata. Phys B Condens Matter 521:162–167

Gadim MR, Navimipour NJ (2017) A new three-level fault tolerance arithmetic and logic unit based on quantum dot cellular automata. Microsyst Technol. https://doi.org/10.1007/s00542-017-3502-x

Heikalabad SR, Asfestani MN, Hosseinzadeh M (2017) A full adder structure without crosswiring in quantum-dot cellular automata with energy dissipation analysis. J Supercomput. https://doi.org/10.1007/s11227-017-2206-4

Barughi YZ, Heikalabad SR (2017) A three-layer full adder/subtractor structure in quantum-dot cellular automata. Int J Theor Phys 56:2848. https://doi.org/10.1007/s10773-017-3453-0

Rad SK, Heikalabad SR (2017) Reversible flip-flops in quantum-dot cellular automata. Int J Theor Phys 56:2990. https://doi.org/10.1007/s10773-017-3466-8

Hosseinzadeh H, Heikalabad SR (2018) A novel fault tolerant majority gate in quantum-dot cellular automata to create a revolution in design of fault tolerant nanostructures, with physical verification. Microelectron Eng 192:52–60. https://doi.org/10.1016/j.mee.2018.01.019

Sadoghifar A, Heikalabad SR (2018) A Content-Addressable Memory structure using quantum cells in nanotechnology with energy dissipation analysis. Phys B Condens Matter 537:202–206. https://doi.org/10.1016/j.physb.2018.02.024

Mariam Z, Keivan N (2012) Ultra-area-efficient reversible multiplier. Microelectr J 43(6):377–385. https://doi.org/10.1016/j.mejo.2012.02.004

Basu S (2014) Realization of combinational multiplier using quantum cellular automata. Int J Comput Appl 99:19

Cho H, Swartzlander EE Jr (2009) Adder and Multiplier Design in Quantum-Dot Cellular Automata. IEEE Trans Comput 58(6):721–727. https://doi.org/10.1109/TC.2009.21

Angizi S, Sarmadi S, Sayedsalehi S, Navi K (2015) Design and evaluation of new majority gate-based RAM cell in quantum-dot cellular automata. Microelectron J 46:43–51

Dharmendra K, Debasis M (2016) Design of a practical fault-tolerant adder in QCA. Microelectr J 53:90–104. https://doi.org/10.1016/j.mejo.2016.04.004

Heikalabad SR, Salimzadeh F, Barughi YZ (2020) A unique three-layer full adder in quantum-dot cellular automata. Comput Electri Eng 86:106735

Norouzi M, Heikalabad SR, Salimzadeh F (2020) A reversible ALU using HNG and Ferdkin gates in QCA nanotechnology. Int J Circuit Theory Appl 48(8):1291–1303

Salimzadeh, Fereshteh, Heikalabad SR, Gharehchopogh FS (2020) Design of a reversible structure for memory in quantum‐dot cellular automata. Int J Circuit Theory Appl

Ahmadpour S-S, Mosleh M, Heikalabad SR (2019) Robust QCA full-adders using an efficient fault-tolerant five-input majority gate. Int J Circuit Theory Appl 47(7):1037–1056

Trailokya N, Ashutosh K, Anand M (2016) An optimal design of full adder based on 5-input majority gate in coplanar quantum-dot cellular automata. Opt Int J Light Electron Opt 127(20):8576–8591. https://doi.org/10.1016/j.ijleo.2016.06.034

Firdous A, Ghulam M, Hossein K, Saeid A, Shaahin A, Keivan N (2016) Towards single layer quantum-dot cellular automata adders based on explicit interaction of cells. J Comput Sci 16:8–15. https://doi.org/10.1016/j.jocs.2016.02.005

Moein K, Reza S-N, Keivan N (2014) A novel design of 8-bit adder/subtractor by quantum-dot cellular automata. J Comput Syst Sci 80(7):1404–1414. https://doi.org/10.1016/j.jcss.2014.04.012

Ahmadpour S-S, Mosleh M, Heikalabad SR (2020) An efficient fault-tolerant arithmetic logic unit using a novel fault-tolerant 5-input majority gate in quantum-dot cellular automata. Comput Electri Eng 82:106548

Ahmadpour S-S, Mosleh M, Heikalabad SR (2020) The design and implementation of a robust single-layer QCA ALU using a novel fault-tolerant three-input majority gate. J Supercomputing 76(12):10155–10185

Waddell J (2012) An overview of binary arithmetic architectures & their implementation in DSP systems.

Walus K, Dysart TJ, Jullien GA, Arief Budiman R (2004) QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3(1):26–31

Srivastava S, Asthana A, Bhanja S, Sarkar S (2011) QCAPRo-an error power estimation tool for QCA circuit design. In: Proceedings of the IEEE International Symposium Circuits System, pp 2377–2380.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kamrani, H., Heikalabad, S.R. Design and implementation of multiplication algorithm in quantum-dot cellular automata with energy dissipation analysis. J Supercomput 77, 5779–5805 (2021). https://doi.org/10.1007/s11227-020-03478-6

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-020-03478-6