Abstract

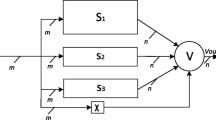

This paper presents a new hybrid fault-tolerant architecture for robustness improvement of digital CMOS circuits and systems. It targets all kinds of errors in combinational part of logic circuits and thus, can be combined with advanced SEU protection techniques for sequential elements while reducing the power consumption. The proposed architecture combines different types of redundancies: information redundancy for error detection, temporal redundancy for soft error correction and hardware redundancy for hard error correction. Moreover, it uses a pseudo-dynamic comparator for SET and timing errors detection. Besides, the proposed method also aims to reduce power consumption of fault-tolerant architectures while keeping a comparable area overhead compared to existing solutions. Results on the largest ISCAS’85 and ITC’99 benchmark circuits show that our approach has an area cost of about 3 % to 6 % with a power consumption saving of about 33 % compared to TMR architectures.

Similar content being viewed by others

Reference

Semiconductor Industry Association (SIA), “International Technology Roadmap for Semiconductors (ITRS)”, 2011

I. Koren, C. M. Krishna, “Fault-Tolerant Systems”, Ed. Organ Kaufmann, 2007

Nicolaidis M, Anghel L, Achouri N (2005) Memory defect tolerance architectures for nanotechnologies”. J of Electronic Testing 21(4):445–455

Chin-Lung Su, Yi-Ting Yeh, Cheng-Wen Wu, “An Integrated ECC and Redundancy Repair Scheme for Memory Reliability Enhancement”, Proc. of the 20th Int. Sym. on Defect and Fault-Tolerance in VLSI Systems (DFT’05), pg. 81–92, 2005

Lyons RE, Vanderkulk W (1962) The use of triple-Modular redundancy to improve computer reliability”. IBM J Res Dev 6(2):200–209

Zhang M, Mitra S, Mak TM, Seifert N, Wang NJ, Shi Q, Kim KS, Shanbhag NR, Patel SJ (2006) Sequential element design with built-in soft error resilience. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 14(12):1368–1378

D. Ernst, N. S. Kim, S. Das, S. Pant, R. Rao, T. Pham, C. Ziesler, D. Blaauw, T. Austin, K. Flautner, T. Mudge, “Razor: A Low-Power Pipeline Based on Circuit-Level Timing Speculation”, Proc. of the 36th Annual IEEE/ACM Int. Sym. on Microarchitecture (MICRO-36), pg. 7–18, December 2003

Das S, Tokunaga C, Pant S, Ma W-H, Kalaiselvan S, Lai K, Bull DM, Blaauw DT (2009) Razor II: In situ error detection and correction for PVT and SER tolerance”. IEEE J of Solid-State Circuits 44(1):32–48

M. E. Imhof, H.-J. Wunderlich, “Soft Error Correction in Embedded Storage Elements”, Proc. of IEEE International On-Line Testing Symposium (IOLTS11), pp. 169–174, 2011

J. Vial, A. Bosio, P. Girard, C. Landrault, S. Pravossoudovitch and A.Virazel, “Using TMR Architectures for Yield Improvement”, Int. Symp.on Defect and Fault-tolerance in VLSI Systems, pp. 7–15, 2008

Vial J, Virazel A, Bosio A, Girard P, Landrault C, Pravossoudovitch S (2009) Is TMR suitable for yield improvement?”. IET Comput Digit Tech 3(6):581–592

D. A. Tran, A. Virazel, A. Bosio, L. Dilillo, P. Girard, S. Pravossoudovitch, H.-J. Wunderlich, “A Hybrid Fault Tolerant Architecture for Robustness Improvement of Digital Circuits”, Proc. of the 20th IEEE Asian Test Symposium (ATS11), pp. 136–141, 2011

P. Shivakumar et al., “Modeling the effect of technology trends on the soft error rate of combinational logic”, Int. Conf. on Dependable Systems and Networks, pp. 389–398, 2002

J. Velamala et al., “Design sensitivity of Single Event Transients in scaled logic circuits”, Design Automation Conf., pp. 694–699, 2011

D.A. Tran, A. Virazel, A. Bosio, L. Dilillo, P. Girard, A. Todri, M.E. Imhof, H.-J. Wunderlich, “A Pseudo-Dynamic Comparator for Error Detection in Fault Tolerant Architectures”, Proc. of the 30th IEEE VLSI Test Symposium (VTS12), pp. 50–55, 2012

M. Nicolaidis, “Graal: a new fault tolerant design paradigm for mitigating the flaws of deep nanometric technologies”, Proc. of IEEE International Test Conference (ITC07), pp.1–10, 2007.

S. Valadimas, Y. Tsiatouhas, A. Arapoyanni, "Timing error tolerance in nanometer ICs", in Proc. of IEEE IOLTS, pp.283-288, 2010

D. J. Palframan, N. S. Kim, M. H. Lipasti, “Time Redundant Parity for Low-Cost Transient Error Detection”, in Proc. of IEEE Design, Automation & Test in Europe, pp. 1–6, March 2011

N. Avirneni, V. Subramanian and A.K. Somani, “Low overhead Soft Error Mitigation techniques for high-performance and aggressive systems”, Dependable Systems & Networks, pp.185-194, 2009

S. Gupta, F. Shuguang Feng, A. Ansari, J. Blome and S. Mahlke, “The StageNet fabric for constructing resilient multicore systems”, Int. Symp. on Microarchitecture, pp.141-151, 2008

J. Yao, H. Shimada, K. Kobayashi, “A Stage-Level Recovery Scheme in Scalable Pipeline Modules for High Dependability”, Int. Workshop on Innovative Architecture for Future Generation High Performance, pp. 21–29, 2010

M. Mehrara, M. Attariyan, S. Shyam, K. Constantinides, V. Bertacco and T. Austin, “Low-Cost Protection for SER Upsets and Silicon Defects”, Design, Automation & Test in Europe Conference, pp. 1–6, 2007

S. Mitra, E. J. McCluskey, “Word-voter: a new voter design for triple modular redundant systems”, Proc. of the IEEE 18th VLSI Test Symposium, pg. 465–470, 2000

Nangate, 45nm Open Cell Library v1.3, http://www.nangate.com, 2009

Zhao W, Cao Y (2007) “Predictive technology model for nano-CMOS design exploration”, ACM Journal on Emerging Technologies in Computing Systems

J. E. Stine, I. Castellanos, M. Wood, J. Henson, F.Love, “FreePDK: An Open-Source Variation-Aware Design Kit”, IEEE Int. Conf. on Microelectronic Systems Education, pg. 173–174, 2007

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: N. A. Touba

This paper is an extended version of previously published papers. Main contributions of this paper with respect to [12, 15] are:

• Integration of the pseudo-dynamic comparator proposed in [15] in the hybrid fault tolerant architecture

• A complete implementation of the initial solution proposed in [12] with respect to timing constraints.

• A complete analysis of the hybrid fault tolerant architecture in terms of power consumption and silicon area.

Rights and permissions

About this article

Cite this article

Tran, D.A., Virazel, A., Bosio, A. et al. A New Hybrid Fault-Tolerant Architecture for Digital CMOS Circuits and Systems. J Electron Test 30, 401–413 (2014). https://doi.org/10.1007/s10836-014-5459-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-014-5459-3