Abstract

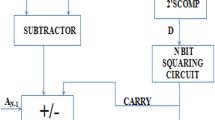

Now a days, an efficient arithmetic operations are important to accomplish the high performance. In every one of these applications, multiplier is an important arithmetic operation. Usually multipliers are utilized to evaluate the square operand. A square operation is faster than a multiplication. This paper proposes a high performance and area efficient square architecture using Anurupya Sutra of Vedic Mathematics. The proposed method is efficient method, which divided the large magnitude number into smaller magnitude numbers and concatenated smaller magnitude numbers. The proposed architecture is synthesized and simulated using Vivado design suite 2018.3 and implemented on Kintex-7 FPGA board. The results revealed a high performance and area efficient compared to a well-known prior art multipliers.

Similar content being viewed by others

References

Pihl, J., & Aas, E. J. (1996). A multiplier and squarer generator for high performance DSP applications. In Proceedings of the 39th Midwest symposium on circuits and systems, (Vol. 1, pp. 109–112).

Chen, T. C. (1971). A binary multiplication based on squaring. IEEE Transaction on Computers, 20(6), 678–680.

Pekmestzi, K. Z., Kalivas, P., & Moshopoulos, N. (2001). Long unsigned number systolic serial multipliers and squares. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 48(3), 316–321.

Dadda, L. (1985). Squares for binary numbers in serial form. In Proceedings of IEEE symposium on computer arithmetic (pp. 173–180).

Chaniotakis, E., Kalivas, P., & Pekmestzi, K. Z. (2005). Long number bit serial squares. In Proceedings of IEEE symposium on computer arithmetic (pp. 29–36).

Liddicoat, A. A., & Flynn, M. J. (2000). Parallel square and cube computations. In 34th Asilomar conference on signals, systems and computers.

Barik, R. K., & Pradhan, M. (2015). Area-time efficient square architecture. AMSE Journal, 20(1), 21–34.

Sharma, R., Kaur, M., & Singh, G. (2015). Design and FPGA implementation of optimized 32-bit Vedic multiplier and square architectures. In International conference on industrial instrumentation and control (ICIC), May 28–30.

Kunchigi, V., Kulkarni, L., & Kulkarni, S. (2014). Low power square and cube architectures using Vedic sutras. In Fifth international conference on signals and image processing.

Barik, R. K., & Pradhan, M. (2017). Efficient ASIC and FPGA implementation of cube architecture. IET Computers & Digital Techniques, 11(1), 43–49.

Kasliwal, P. S., Patil, B. P., & Gautam, D. K. (2011). Performance evaluation of squaring operation by Vedic Mathematics. IETE Journal of Research, 57(1), 39–41.

Thapliyal, H., Kotiyal, S., & Srinivas, M. B. (2005). Design and analysis of a novel parallel square and cube architecture based on ancient Indian Vedic Mathematics. In 48th midwest symposium on circuits and systems (pp. 1462–1465).

Sethi, K., & Panda, R. (2015). Multiplier less high-speed squaring circuit for binary numbers. International Journal of Electronics, 102(3), 433–443.

http://www.xilinx.com/products/boards-and-kits/ek-k7-kc705-g.html

Kavehl, M., Khishe, M., & Mosavi, M. R. (2018). Design and implementation of a neighborhood search biogeography-based optimization trainer for classifying sonar dataset using multi-layer perceptron neural network. Analog Integrated Circuits and Signal Processing. https://doi.org/10.1007/s10470-018-1366-3.

Beechu, N. K. R., et al. (2017). System level fault–tolerance core mapping and FPGA-based verification of NoC. Microelectronics Journal, 70, 16–26.

Beechu, N. K. R., et al. (2018). Hardware implementation of fault tolerance NoC core mapping. Telecommunication Systems, 68(4), 621–630.

Beechu, N. K. R., et al. (2017). High-performance and energy-efficient fault–tolerance core mapping in NoC. Sustainable Computing: Informatics and Systems, 16, 1–10.

Naresh Kumar Reddy, B., & Sireesha (2019). An energy-efficient core mapping algorithm on network on chip (NoC). In VDAT, CCIS 892 (pp. 631–640).

Naresh Kumar Reddy, B., Suresh, N., Ramesh, J. V. N., Pavithra, T., Krupa Bahulya, Y., Edavoor, P. J., & Janaki Ram, S. (2015). An efficient approach for design and testing of FPGA programming using LabVIEW. In International conference on advanced computing, networking and informatics: ICACNI.

Boddu, V. S., et al. (2016). Low-power and area efficient N-bit parallel processors on a chip. In IEEE India Council international conference (INDICON).

Chua, C., Kumar, R. B. N., & Sireesha, B. (2017). Design and analysis of low-power and area efficient N-bit parallel binary comparator. Analog Integrated Circuits and Signal Processing, 92, 225–231.

Acknowledgements

The author express their sincere gratitude to anonymous reviewers and the editor for their comments and suggestions towards improvement of this manuscript.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Reddy, B.N.K. Design and implementation of high performance and area efficient square architecture using Vedic Mathematics. Analog Integr Circ Sig Process 102, 501–506 (2020). https://doi.org/10.1007/s10470-019-01496-w

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01496-w