Abstract

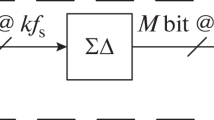

A hybrid (analog/digital) architecture is proposed to implement a robust high-resolution delta-sigma modulator with a single-bit output. The system contains a low-order multi-bit analog noise-shaping loop, followed by a scaling block and a high-order single-bit digital modulator. The combination simplifies the realization of the analog modulator, and it allows the use of most of its full-scale input range.

Similar content being viewed by others

References

Yao, L., Steyaert, M., & Sansen, W. (2004). A 1-V 140-uW 88-dB audio sigma-delta modulator in 90-nm CMOS. IEEE Journal of Solid-State Circuits, 39, 1809–1818.

Nguyen, K., Adams, R., Sweetland, K., & Chen, H. (2005). A 106-dB SNR hybrid oversampling analog-to-digital converter for digital audio. IEEE Journal of Solid-State Circuits, 40, 2408–2415.

Ahn, G., et al. (2005). A 0.6-V 82-dB delta-sigma audio ADC using switched-RC integrators. IEEE Journal of Solid-State Circuits, 40, 2398–2407.

Schreier, R., & Temes, G. C. (2004). Understanding delta-sigma data converters. New York: Wiley.

Baird, R. T., & Fiez, T. S. (1995). Improved ΔΣ DAC linearity using data weighted averaging. In Proc. IEEE Int. Symp. Circuits and Systems, Vol. 1, pp. 13–16, May 1995.

Silva, J., Moon, U., Steensgaard, J., & Temes, G. (2001). Wideband low-distortion delta-sigma ADC topology. Electronics Letters, 37(12), 737–738.

Schreier, R. The Delta-Sigma Toolbox 7.2′′, http://www.mathworks.com/matlabcentral/fileexchange/loadFile.do?objectId=19.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wang, Y., Hamashita, K. & Temes, G.C. Hybrid delta-sigma ADC. Analog Integr Circ Sig Process 63, 293–298 (2010). https://doi.org/10.1007/s10470-009-9397-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-009-9397-4