Abstract

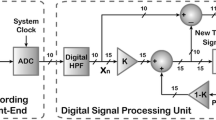

We present the design of an integrated neural interface intended for multi-channel neural recording. The design features a mixed-signal part that handles neural signal conditioning, digitization, time-division multiplexing, and a digital module providing control, absolute threshold detection, extraction of spikes, and serial communications towards a host interface. The detection and extraction strategy preserves the entire neuronal spike waveshapes by means of synchronized internal data buffering. This bandwidth reduction scheme prompts for better waveform sorting results and improved performance in prosthetic applications. Both parts of the presented neural interface were fabricated separately in a CMOS 0.18 μm process. The whole neural interface features 16 channels for validation, but, the proposed approach is scalable to larger channel counts. The performance of the implemented neural interface was validated on testbench with synthetic neural waveforms. It features a power consumption of 138 μW per channel and a size of 2.304 mm2, and achieves a bandwidth reduction factor of up to 48.

Similar content being viewed by others

References

Olsson, R. H., III., & Wise, K. D. (2005). A three-dimensional neural recording microsystem with implantable data compression circuitry. IEEE Journal of Solid-State Circuits, 40, 2796–2804.

Harrison, R. R., Watkins, P. T., Kier, R. J., Lovejoy, R. O., Black, D. J., Greger, B., et al. (2007). A low-power integrated circuit for a wireless 100-electrode neural recording system. IEEE Journal of Solid-State Circuits, 42, 123–133.

Harrison, R. R. (2003). A low-power integrated circuit for adaptive detection of action potentials in noisy signals. In The 25th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (pp. 3325–3328).

Sodagar, A. M., Wise, K. D., & Najafi, K. (2007). A fully integrated mixed-signal neural processor for implantable multichannel cortical recording. IEEE Transactions on Biomedical Engineering, 54, 1075–1088.

Perelman, Y., & Ginosar, R. (2007). An integrated system for multichannel neuronal recording with spike/LFP separation, integrated A/D conversion and threshold detection. IEEE Transactions on Biomedical Engineering, 54, 130–137.

Rizk, M., Obeid, I., Callender, S. H., & Wolf, P. D. (2007). A single-chip signal processing and telemetry engine for an implantable 96-channel neural data acquisition system. Journal of Neural Engineering, 4, 309–321.

Gosselin, B., & Sawan, M. (2007). A low-power integrated neural interface with digital spike detection and isolation. In The 14th IEEE International Conference on Electronics, Circuits and Systems (pp. 1412–1415).

Ayoub, A. E., Gosselin, B., & Sawan, M. (2007). A microsystem integration platform dedicated to build multi-chip-neural interfaces. In 29th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (pp. 6604–6607).

Gosselin, B., Sawan, M., & Chapman, C. A. (2007). A low-power integrated bioamplifier with active low-frequency suppression. IEEE Transactions on Biomedical Circuits and Systems, 1, 184–192.

Robert, P.-Y., Gosselin, B., & Sawan, M. (2006). An ultra-low-power successive-approximation-based ADC for implantable sensing devices. In The 2006 Midwest Symposium on Circuits and Systystems, 1, 7–11.

Wood, F., Black, M. J., Vargas-Irwin, C., Fellows, M., & Donoghue, J. P. (2004). On the variability of manual spike sorting. IEEE Transactions on Biomedical Engineering, 51, 912–918.

Zumsteg, Z. S., Kemere, C., O’Driscoll, S., Santhanam, G., Ahmed, R. E., Shenoy, K. V., et al. (2005). Power feasibility of implantable digital spike sorting circuits for neural prosthetic systems. IEEE Transactions on Neural Systems and Rehabilitation Engineering, 13, 272–279.

Acknowledgment

The authors acknowledge the design and testing tools from CMC Microsystems, and thank Prof. C. A. Chapman, (Concordia University, Mtl.), for providing the neural waveforms. Also, we acknowledge the contribution of J. -F. Roy and P.-Y. Robert to this work, and we thank Laurent Mouden for realizing the chip on board assembly.

Author information

Authors and Affiliations

Corresponding author

Additional information

This work was supported in part by the Natural Sciences and Engineering Research Council of Canada and the Canadian Research Chair on Smart Medical Devices.

Rights and permissions

About this article

Cite this article

Gosselin, B., Sawan, M. A low-power integrated neural interface with digital spike detection and extraction. Analog Integr Circ Sig Process 64, 3–11 (2010). https://doi.org/10.1007/s10470-009-9371-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-009-9371-1