Abstract

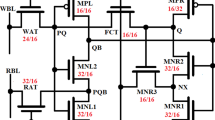

This paper proposes a novel subthreshold 10T SRAM cell. The proposed design removes the half-select issue which is a problem in SRAM array as observed in the case of conventional 6T and 8T cells. Since the proposed cell is free from half-select disturb, bit-interleaving scheme can be implemented. A bit-interleaved architecture helps to reduce errors in multiple bits of a single word. This makes the proposed design immune to soft error caused by α particles or high-energy cosmic rays. The proposed cell uses data-dependent stack PMOS switching scheme (DSPS) to reduce the write access time and improve the write-ability. A single-ended read decoupled scheme used to perform read operation enhances the read stability. Various design metrics of the proposed SRAM cell have been compared with previously proposed cells such as SBI9T, DF9T and UDVS10T. The proposed cell shows 1.07×, 2.89× and 13.78× improvement in write access time while writing ‘0’ as compared to the SBI9T, DF9T and UDVS10T, respectively at a V DD of 0.4 V. The proposed cell shows lesser spread in write delay as compared to DF9T cell, which signifies lower variability. There is 8.4, 10.3 and 6.5 % improvement in WSNM when compared to the three cells mentioned above, respectively. Also, 27.3 and 2.02 % improvements can be observed in RSNM when compared to the SBI9T and DF9T at a supply voltage of 0.4 V. RSNM of UDVS10T is same as that of the proposed design. As far as power consumption is concerned, the proposed design consumes 1.38× lesser read power as compared to UDVS10T and 1.67× and 5.02× lesser write power as compared to DF9T and UDVS10T respectively. The proposed design shows 1.8 % improvement in read current variability when compared to DF9T. Lastly, the proposed cell shows 2.21× and 5.25× higher I READ/I LEAK as compared to DF9T and UDVS10T.

Similar content being viewed by others

References

Azam T, Cheng B, Roy S, Cumming DRS (2010) Robust asymmetric 6T-SRAM cell for low-power operation in nano-CMOS technologies. Electron Lett 46(4):273–274

Carlson AE (2008) Device and circuit techniques for reducing variation in nanoscale SRAM. Ph.D. dissertation, University of California Berkeley, Berkeley, CA

Chang L et al (2008) An 8 T-SRAM for variability tolerance and low voltage operation in high-performance caches. IEEE J Solid-State Circuit 43(4):956–963

Chang IJ, Kim J-J, Park SP, Roy K (2009) A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS. IEEE J Solid-State Circuits 44(2):650–658

Chang M-F, Chang S-W, Chou P-W, Wu W-C (2011) A 130 mV SRAM with expanded write and read margins for subthreshold applications. IEEE J Solid-State Circuits 46(2):520–529

Chang MF et al (2012a) A differential data-aware power-supplied (D2AP) 8 T SRAM cell with expanded write/read stabilities for low VDDmin applications. IEEE J Solid-State Circuit 45(6):1234–1245

Chang MH, Chiu Y-T, Hwang W (2012b) Design and iso-area Vmin analysis of 9T subthreshold SRAM with bit-interleaving scheme in 65-nm CMOS. IEEE Trans Circuits Syst II Exp Briefs 59(7):429–433

Chen J et al (2012) An ultra-dynamic voltage scalable (U-DVS) 10T SRAM with bit-interleaving capability. In: IEEE symposium on circuits and systems, May 2012, pp 1835–1838

Do A-T et al (2011) An 8T differential SRAM with improved noise margin for bit-interleaving in 65 nm CMOS. IEEE Trans Circuits Syst I 58(6):1252–1263

Hamming RW (1950) Error detecting and error correcting codes. Bell Syst Tech J 29:147–160

Hazucha P et al (2003) Neutron soft error rate measurements in 90-nm CMOS process and scaling trends in SRAM from 0.25-μm to 90-nm generation. In: IEDM technical digest, Dec 2003, pp 21.5.1–21.5.4

Islam A, Hasan M (2012a) Leakage characterization of 10T SRAM cell. IEEE Trans Electron Devices 59(3):631–638

Islam A, Hasan M (2012b) A technique to mitigate impact of process, voltage and temperature variations on design metrics of SRAM cell. Microelectron Reliab 52(2):405–411

Islam A, Hasan M, Arslan T (2012) Variation resilient subthreshold SRAM cell design technique. Int J Electron 99(9):1223–1237

Joshi RV et al (2011) A novel column-decoupled 8 T cell for low- power differential and domino-based SRAM design. IEEE Trans Very Large Scale Integr (VLSI) Syst 19(5):869–882

Khayatzadeh M, Lian Yong (2014) Average 8-T differential-sensing subthreshold SRAM with bit interleaving and 1 k bits per bitline. IEEE Trans Very Large Scale Integr (VLSI) Syst 22(5):971–982

Kulkarni JP, Roy K (2012) Ultralow-voltage process-variation-tolerant Schmitt-trigger-based SRAM design. IEEE Trans Very Large Scale Integr (VLSI) Syst 20(2):319–332

Kulkarni JP, Kim K, Roy K (2007) A 160 mV robust Schmitt trigger based subthreshold SRAM. IEEE J Solid-State Circuits 42(10):2303–2313

Markovic D et al (2010) Ultralow-Power design in near-threshold region. In: Proceedings of the IEEE, vol 98(2), pp 237–252. Online. http://ptm.asu.edu/. Accessed 21 Mar 2015

Narsimham S (2013) Hardware Trojan detection by multiple-parameter side-channel analysis. IEEE Trans Comput 62(11):2183–2195

Pasandi G, Fakhraie SM (2014) An 8T low-voltage and low-leakage half-selection disturb-free SRAM using bulk-CMOS and FinFETs. IEEE Trans Electron Devices 61(7):2357–2363

Rabaey JM, Chandrakasan AP, Nikolic B (2003) Digital integrated circuits: a design perspective, 2nd edn. Prentice-Hall, New Delhi

Sinangil M. E., Verma N. and Chandrakasan A. P. (2009) A 45 nm 0.5 V 8T column-interleaved SRAM with on-chip reference selection loop for sense-amplifier. In: Proceedigs of the IEEE Asian solid-state circuits conference, Nov 2009, pp 225–228

Sun Y, Jiao H, Kursun V (2015) A novel robust and low-leakage SRAM cell with nine carbon nanotube transistors. IEEE Trans Very Large Scale Integr (VLSI) Syst 23(9):1729–1739

Tu MH et al (2012) A single-ended disturb-free 9T subthreshold SRAM with cross-point data aware write word-line structure, negative bit-line, and adaptive read operation timing tracing. IEEE J Solid-State Circuits 47(6):1469–1482

Vaddi R, Dasgupta S, Agarwal RP (2010) Device and circuit co-design robustness studies in the subthreshold logic for ultralow-power applications for 32 nm CMOS. IEEE Trans Electron Devices 57(3):654–664

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sinha, A., Islam, A. Low-power half-select free single-ended 10 transistor SRAM cell. Microsyst Technol 23, 4133–4144 (2017). https://doi.org/10.1007/s00542-016-3032-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-016-3032-y