Abstract

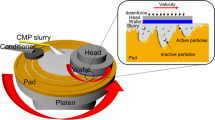

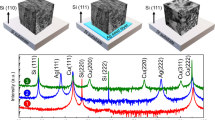

In this study, (100)-orientation silicon wafer coated with TiN barrier is catalyzed by a Pd/Sn colloid, which serves as an activator for electroless copper deposition. After activation, electroless deposition of Cu occurs on the catalytic surface. The coverage of the Cu deposit reaches 100% and the adsorptive amount of Pd is greatly increased by the conditioning process. The correlation between deposition rate, resistivity, morphology, crystal structure, and composition of the deposit when varying the temperature of the plating bath is discussed. The deposition rate of Cu is monitored by both the electrochemical method and the profilometer (α-step), while the other properties of the deposit are measured by four-point probe, scanning electron microscopy (SEM), x-ray diffraction (XRD), and Auger electron microscopy (AES). Deposition at 70°C is favorable due to the higher deposition rate, lower resistivity, less impurities, and more preferred orientation in the crystal structure than that at lower temperature. Problems regarding adhesion and high resistivity can be greatly mitigated via 400°C thermal annealing. The resistivity of Cu can be reduced to 2.2 μΩcm. Moreover, trenches of 1 µm and 0.25 µm on patterned wafer have been successfully filled by electroless deposition of Cu with the aid of surfactant C12.

Similar content being viewed by others

References

J.D. Plummer, M.D. Deal, and P.B. Griffin, Silicon VLSI Technology (Englewood Cliffs, NJ: Prentice-Hall, Inc., 2000), pp. 570–572.

P.C. Andricacos, Interface 8, 32 (1999).

P.C. Andricacos, C. Uzoh, J.O. Dukovic, J. Horkans, and H. Deligianni, IBM J. Res. Develop. 42, 567 (1998).

V.M. Dubin, C.H. Ting, and R. Cheung, VMIC Conf. (1997).

M.J. Desilva, V. Dubin, and Y. Shcham-Diamand, J. Mater. Res. 11, 607 (1996).

B. Zhao and P.K. Vasudev, J. Mater. Res. 11, 179 (1996).

V.M. Dubin and Y. Shcham-Diamand, J. Electrochem. Soc. 144, 898 (1997).

V.M. Dubin, J. Electrochem. Soc. 139, 633 (1992).

H.H. Hsu, K.H. Lin, S.J. Lin, and J.W. Yeh, J. Electrochem. Soc. 148, C47 (2001).

H.H. Hsu, C.W. Ting, S.J. Lin, and J.W. Yeh, J. Electrochem. Soc. 149, C143 (2002).

E.D. D’Ottavio, U.S. patent 3,532,518 (1970); U.S. patent 3,650,913 (1972).

M.W. Jawitz, Printed Circuit Board Materials Handbook (New York, NY: McGraw-Hill Companies, Inc., 1997), pp. 23.1–23.5.

T. Osaka, H. Takematsu, and K Nihei, J. Electrochem. Soc. 148, C162 (1980).

C.S. Yang, C.C. Chen, Y.Y. Wang, and C.C. Wan, J. Electrochem. Soc. 143, 3521 (1996).

Y. Shcham-Diamand, V.M. Dubin, and M. Angyal, Thin Solid Film 262, 93 (1995).

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Fong, H.P., Wu, Y., Wang, Y.Y. et al. Electroless Cu deposition process on TiN for ULSI interconnect fabrication via Pd/Sn colloid activation. J. Electron. Mater. 32, 9–17 (2003). https://doi.org/10.1007/s11664-003-0246-4

Received:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/s11664-003-0246-4